ニュース 世界初のミックスドシグナルベースバンド復調回路による 20Gb/s QPSK無線伝送技術を開発

2024.04.23 リリース

令和6年4月23日

ザインエレクトロニクス株式会社

国立研究開発法人情報通信研究機構

国立大学法人広島大学

世界初のミックスドシグナルベースバンド復調回路による20Gb/s QPSK無線伝送技術を開発

【開発のポイント】

ミックスドシグナル技術を用いて超高速情報伝送の実現と電力効率の改善へ

無線通信に用いられるベースバンド復調回路(注1)は通常、高速・高分解能ADC(注2)と大規模DSP(注3)で構成されています。従来の構成を用いて数十Gb/sを超える高速な通信を行う場合、ADCとDSPへの要求性能が高くなり電力効率が悪化します。

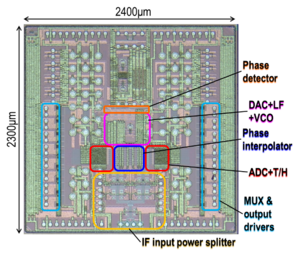

今回、ミックスドシグナル(注4)技術を用いて高速・低分解能ADCと小規模DSPからなる世界初のベースバンド復調回路を、ザインエレクトロニクス株式会社、国立研究開発法人情報通信研究機構(NICT(エヌアイシーティー))、国立大学法人広島大学が共同で開発しました。これにより数十Gb/sを超える超高速通信を実現しながらも、電力効率が改善することで大幅な電力削減が見込まれます。

ベースバンド復調回路を搭載した受信用半導体で20Gb/s QPSK通信が可能に

ベースバンド復調回路を搭載した受信用半導体とロジック回路を搭載したFPGA(注5)を開発し20Gb/s QPSK(注6) 変調された電気信号の受信を実現しました。FPGAに実装した機能は実用化の際にはベースバンド受信用半導体に統合します。

【概要】

ザインエレクトロニクス、NICT、広島大学は共同で、総務省研究開発プロジェクトの一環で、世界初のミックスドシグナル広帯域ベースバンド回路による毎秒20ギガビットの超高速情報伝送を実現しました。ザインエレクトロニクスは設計・測定全般を、広島大学大学院先進理工系科学研究科の藤島実教授らは設計・測定についての議論を、NICTは測定についての議論や測定補助をそれぞれ担当しました。

この半導体回路は、キャリア(注7)周波数をシンボル(注8)・キャリア周波数の整数倍にすることで回路を簡素化することができます。キャリア、タイミング(注9)とデータ復元機能を統合する独自の回路構成 (ミックスドシグナルコスタス・ループ) を用いることで超高速情報伝送を実現しました。高速・低解像度ADCは8相タイムインターリーブ(回路全体で出力を8倍速化)毎秒40ギガサンプルの3bit ADCを実装し、これにFPGAを用いてデータを復元することで実現しました。

本研究成果は、2024 IEEE Custom Integrated Circuits Conference (CICC、2024年4月21日~4月24日、米国コロラド州デンバー)で発表を行いました[1]。

【今後の展開】

今回の研究成果により、ミックスドシグナル型アーキテクチャを通じて、より高性能でありながらも、エネルギー効率にも優れた回路実装への道を拓くものとなりました。

【用語解説】

(注1)ベースバンド復調回路: 変調されて無線送信されたベースバンド信号(デジタル信号)を、受信機側で元のベースバンド信号に復調する回路

(注2)ADC: アナログ・デジタル変換回路

(注3)DSP: デジタルシグナルプロセッサ

(注4)ミックスドシグナル: アナログ信号とデジタル信号の両方を取り扱う回路

(注5)FPGA: Field Programmable Gate Array

(注6)QPSK: Quaternary Phase Shift Keying (四位相偏移変調) であり、一度の変調で4値 (2ビット)を表現できる変調方式。

(注7)キャリア: 信号を送受信するために使用される電波

(注8)シンボル:情報を電波に載せる時の変調信号の単位

(注9)タイミング: データ生成に必要な時間情報のこと

【総務省研究開発プロジェクトの背景】

総務省では、新たな電波利用ニーズの拡大に対応するため、周波数のひっ迫状況を緩和し、電波の有効利用を目的とした電波資源拡大のための研究開発を行い、超大容量無線通信を実現可能とし、新たな周波数帯の利用を促進することにより電波資源の拡大に資することを目標としております。

本成果の一部は総務省電波資源拡大のための研究開発(JPJ000254)によるものです。

課題名:テラヘルツ波による超大容量無線LAN伝送技術の研究開発

課題イ トランシーバ技術の研究開発

参考文献

Shunichi Kubo1, Yuji Gendai1, Satoshi Miura1, Shinsuke Hara2,3, Satoru Tanoi2, Akifumi Kasamatsu2, Takeshi Yoshida3, Satoshi Tanaka3, Shuhei Amakawa3, Minoru Fujishima3, “A 20Gb/s QPSK Receiver with Mixed-Signal Carrier, Timing, and Data Recovery Using 3-bit ADCs ,” 2024 IEEE Custom Integrated Circuits Conference.

1THine Electronics, Inc., 2National Institute of Information and Communications Technology, 3Hiroshima University

【報道関係者 お問い合わせ先】

ザインエレクトロニクス株式会社 取締役総務部長 山本 武男

電話:03-5217-6660 E-mail:investors@thine.co.jp

国立研究開発法人情報通信研究機構

<研究に関すること>

未来ICT研究所小金井フロンティア研究センター 研究センター長 笠松 章史

E-mail:kasa@nict.go.jp

<広報に関すること>

広報部 報道室 E-mail:publicity@nict.go.jp

国立大学法人広島大学

<研究に関すること>

大学院先進理工系科学研究科 教授 藤島 実

電話:082-424-6269 E-mail:fuji@hiroshima-u.ac.jp

<広報に関すること>

広報室 電話:082-424-3749 E-Mail:koho@office.hiroshima-u.ac.jp