THine Value GPIOとI2Cを束ねて送るシリアル・トランシーバ。ユーザー・メリットが大きい2つの変更点を解説

2025.09.29

- 記事

- コラム

本稿は、シリアル・トランシーバIC「IOHA:B」を全2回で解説する記事の後編である。前編では、後継品「THCS253A/THCS254A」の特徴に加えて、従来品「THCS251」からの変更点である「GPIO(汎用入出力)に加えてI2Cに対応したこと」を紹介し、ユーザーが得られるメリットを説明した。後編では、その変更点をより詳しく解説するとともに、もう1 つの変更点である「同期/非同期モードの導入」について紹介する。

I/Oを自由にカスタマイズ

今回の後継品であるTHCS253A/THCS254Aの基本機能は、数多くの信号ラインで送っていたパラレル伝送を、わずか2ペアの差動ラインによるシリアル伝送に置き換えるというもの。例えば、34本もある信号ラインを、本製品を使えばわずか4本に削減できる。削減率は88%と高い。しかも配線ケーブルの重量を減らせる上に、伝送距離を延ばすことができる。前編でも述べた通り、ユーザーが得られるメリットは大きい。

ただしこの基本機能自体は、従来品のTHCS251/THCS252とまったく同じであり、新規性はない。THCS253A/THCS254Aは、この基本機能を従来品から継承しながら、大きな変更を2つ加えた。それが冒頭で紹介したGPIOに加えてI2Cに対応したことと、同期/非同期モードの導入である。

まずは、1つ目の変更であるGPIOに加えてI2Cに対応したことについて詳しく解説する。この変更の中身は、すでに前編で簡単に紹介している。すなわち、複数本のGPIOに加えて、1系統もしくは2系統のI2Cも束ねてシリアル伝送できるというものだ。これによってユーザーは極めて大きなメリットを得られる。なぜならば、I2Cを使って内部レジスタを書き換えることで、高い自由度でI/O(入出力インターフェース)部をカスタマイズできるようになるからである。

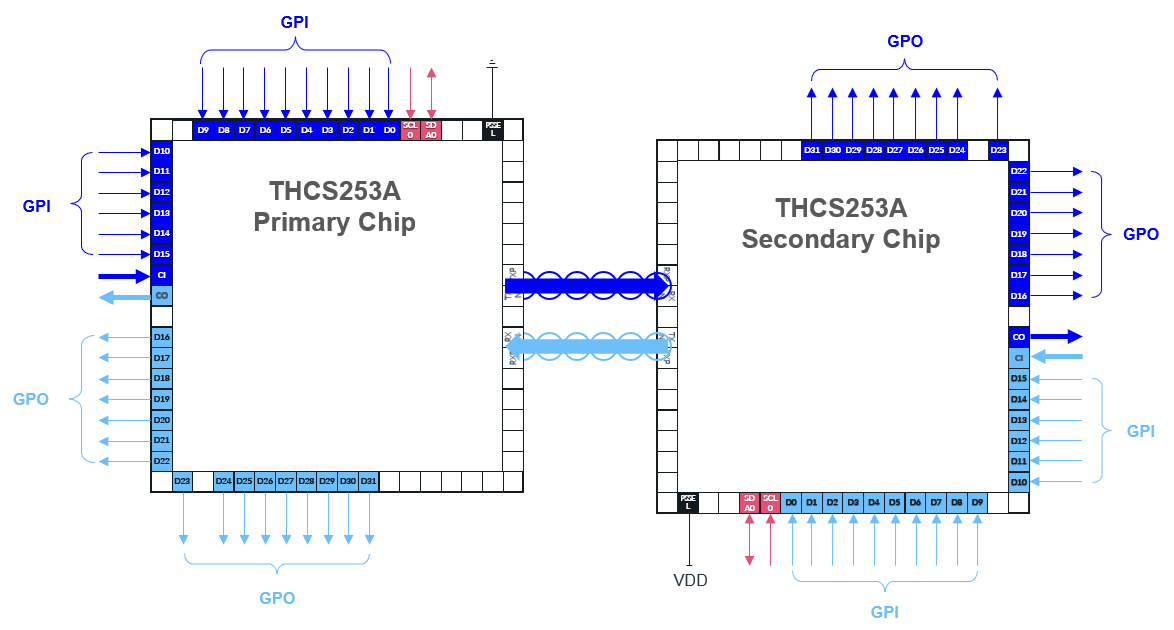

具体的に説明しよう。THCS253A/THCS254Aを電子機器に適用する場合、同じチップ(IC)を2個用意して、一方をプライマリ・チップに、もう一方をセカンダリ・チップにPSSEL端子を使って指定する。扱えるGPIOの本数はTHCS253Aが最大32本、THCS254Aが最大20本である。例えば、THCS253Aの場合、デフォルトでGPI(汎用入力)が16本と、GPO(汎用出力)が16本という端子構成に設定されている(図1)。

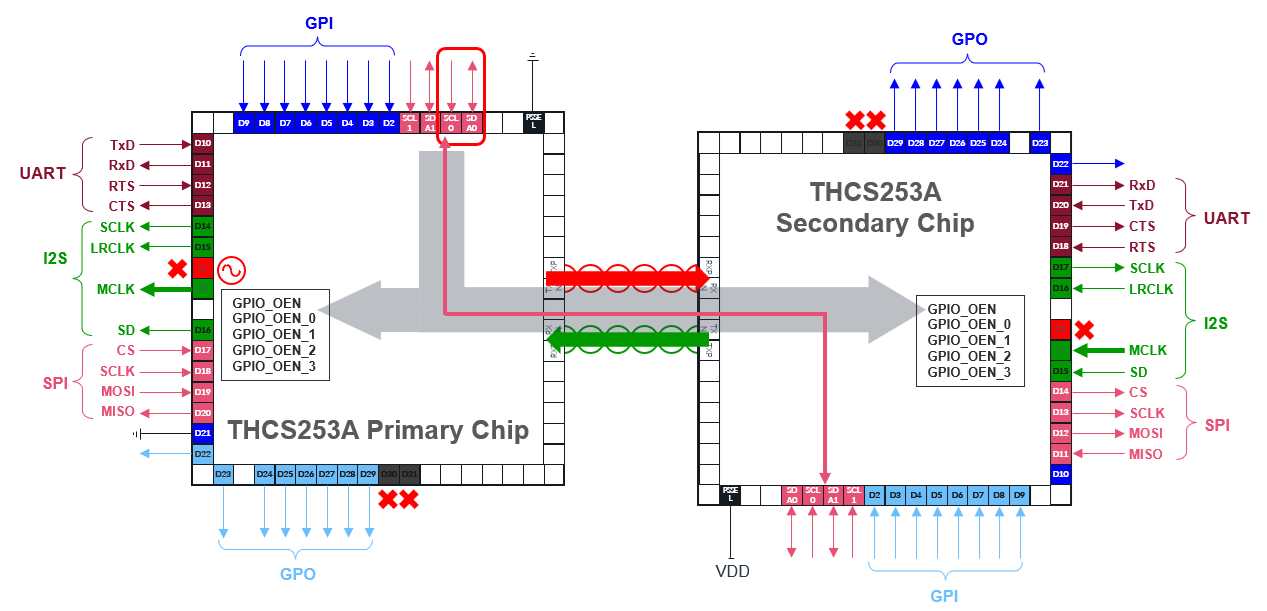

このGPIとGPOの本数は、ユーザーが自由に設定できる。I2Cを介して内部レジスタを書き換えることで、1端子ごとにGPIもしくはGPOに指定できるからだ。図2はその具体例である(各端子をGPIOや I2S、SPI、UARTの入力/出力にアサインした例)。

従来品のTHCS251/THCS252でもGPIとGPOの本数をユーザーが指定できたが、それらの本数比率を4段階で選べるだけにとどまっていた。つまり、I/O部をカスタマイズできる自由度は、今回のTHCS253A/THCS254Aに比べると低かった。

このI/O部のカスタマイズが大きな効果を発揮するのは、設計対象の電子機器への新機能の追加などで急な設計変更が発生した場合のほか、将来のモデルチェンジや機能追加に備えて設計の共通化を図る場合などである。一般に設計変更やモデルチェンジ、機能追加などを実行すると、新機能を実現する回路が増えてI/O端子の本数が増加したり、I/O端子の位置関係が変わったりすることなどが起こり得る。従来品では、I/O部のカスタマイズの自由度が高くなかったため、場合によっては信号伝送路などのハードウエアの再設計が必要となることがあった。しかし今回の後継品を採用すれば、非常に高い自由度でI/Oをカスタマイズでき、設計変更や機能追加などに極めて柔軟に対処できる。このため、ハードウエアの再設計を高い確率で避けられる。設計期間が延びたり、設計コストが増えたりする事態を回避できるわけだ。

ただしこの基本機能自体は、従来品のTHCS251/THCS252とまったく同じであり、新規性はない。THCS253A/THCS254Aは、この基本機能を従来品から継承しながら、大きな変更を2つ加えた。それが冒頭で紹介したGPIOに加えてI2Cに対応したことと、同期/非同期モードの導入である。

まずは、1つ目の変更であるGPIOに加えてI2Cに対応したことについて詳しく解説する。この変更の中身は、すでに前編で簡単に紹介している。すなわち、複数本のGPIOに加えて、1系統もしくは2系統のI2Cも束ねてシリアル伝送できるというものだ。これによってユーザーは極めて大きなメリットを得られる。なぜならば、I2Cを使って内部レジスタを書き換えることで、高い自由度でI/O(入出力インターフェース)部をカスタマイズできるようになるからである。

具体的に説明しよう。THCS253A/THCS254Aを電子機器に適用する場合、同じチップ(IC)を2個用意して、一方をプライマリ・チップに、もう一方をセカンダリ・チップにPSSEL端子を使って指定する。扱えるGPIOの本数はTHCS253Aが最大32本、THCS254Aが最大20本である。例えば、THCS253Aの場合、デフォルトでGPI(汎用入力)が16本と、GPO(汎用出力)が16本という端子構成に設定されている(図1)。

図1 デフォルト時のI/O設定(THCS253A)

このGPIとGPOの本数は、ユーザーが自由に設定できる。I2Cを介して内部レジスタを書き換えることで、1端子ごとにGPIもしくはGPOに指定できるからだ。図2はその具体例である(各端子をGPIOや I2S、SPI、UARTの入力/出力にアサインした例)。

図2 I2C経由で内部レジスタを書き換えI/Oをカスタマイズした具体例

従来品のTHCS251/THCS252でもGPIとGPOの本数をユーザーが指定できたが、それらの本数比率を4段階で選べるだけにとどまっていた。つまり、I/O部をカスタマイズできる自由度は、今回のTHCS253A/THCS254Aに比べると低かった。

このI/O部のカスタマイズが大きな効果を発揮するのは、設計対象の電子機器への新機能の追加などで急な設計変更が発生した場合のほか、将来のモデルチェンジや機能追加に備えて設計の共通化を図る場合などである。一般に設計変更やモデルチェンジ、機能追加などを実行すると、新機能を実現する回路が増えてI/O端子の本数が増加したり、I/O端子の位置関係が変わったりすることなどが起こり得る。従来品では、I/O部のカスタマイズの自由度が高くなかったため、場合によっては信号伝送路などのハードウエアの再設計が必要となることがあった。しかし今回の後継品を採用すれば、非常に高い自由度でI/Oをカスタマイズでき、設計変更や機能追加などに極めて柔軟に対処できる。このため、ハードウエアの再設計を高い確率で避けられる。設計期間が延びたり、設計コストが増えたりする事態を回避できるわけだ。

出力形式とフィルタをカスタマイズ可能

さらにI2Cを活用して内部レジスタを書き換えれば、出力形式とデジタル・ノイズ・フィルタについてもユーザーが設定できる。出力形式の選択肢はプッシュプル(Push-pull)とオープン・ドレイン(Open Drain)の2種類。デジタル・ノイズ・フィルタは端子ごとに有無を設定できるほか、フィルタの段数(次数)もユーザーが選べる。ただし、段数(次数)は端子ごとに設定できない。例えば3段(3次)と決めれば、各端子に適用されるフィルタの段数(次数)はすべて3段(3次)になる。

後継品では、デフォルトで1系統のI2Cを搭載しているが、内部レジスタを書き換えることでGPIOの2本をI2Cに割り当てて2系統に増やせる仕組みを用意した。設計対象となる電子機器によっては、SoCが備えるI2C系統に加えて、外部から購入して組み込むタッチパネルやNFC(Near Field Communication)などのモジュール/ユニットにも別のI2C系統が搭載されているケースがある。こうしたケースに、I2Cを2系統に増やせる仕組みは便利だ。なお、I2Cを2系統(信号本数は4本)にした場合、THCS253AのGPIOは30本、THCS254Aは18本になる。

後継品では、デフォルトで1系統のI2Cを搭載しているが、内部レジスタを書き換えることでGPIOの2本をI2Cに割り当てて2系統に増やせる仕組みを用意した。設計対象となる電子機器によっては、SoCが備えるI2C系統に加えて、外部から購入して組み込むタッチパネルやNFC(Near Field Communication)などのモジュール/ユニットにも別のI2C系統が搭載されているケースがある。こうしたケースに、I2Cを2系統に増やせる仕組みは便利だ。なお、I2Cを2系統(信号本数は4本)にした場合、THCS253AのGPIOは30本、THCS254Aは18本になる。

同期モードと非同期モードの両方が使える

次に、もう1つの大きな変更である同期/非同期モードの導入について説明しよう。従来品であるTHCS251/THCS252は同期モードしか使えなかったが、今回のTHCS253A/THCS254Aでは同期モードと非同期モードの両方を利用できるようになった。使用するモードは、セカンダリ・チップの端子設定でユーザーが選択できる。

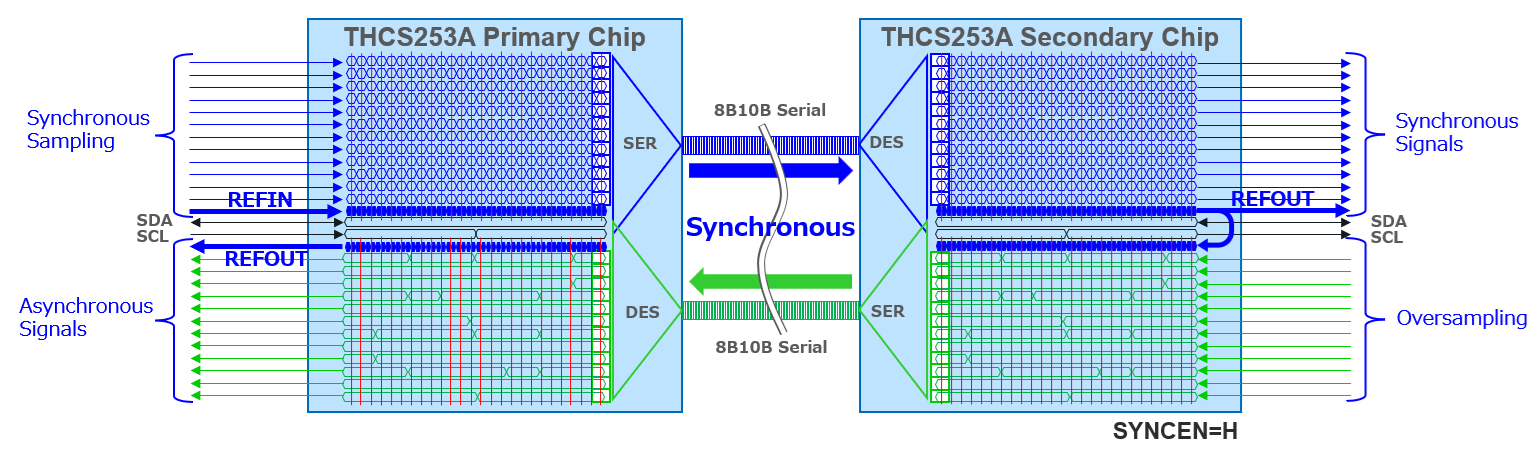

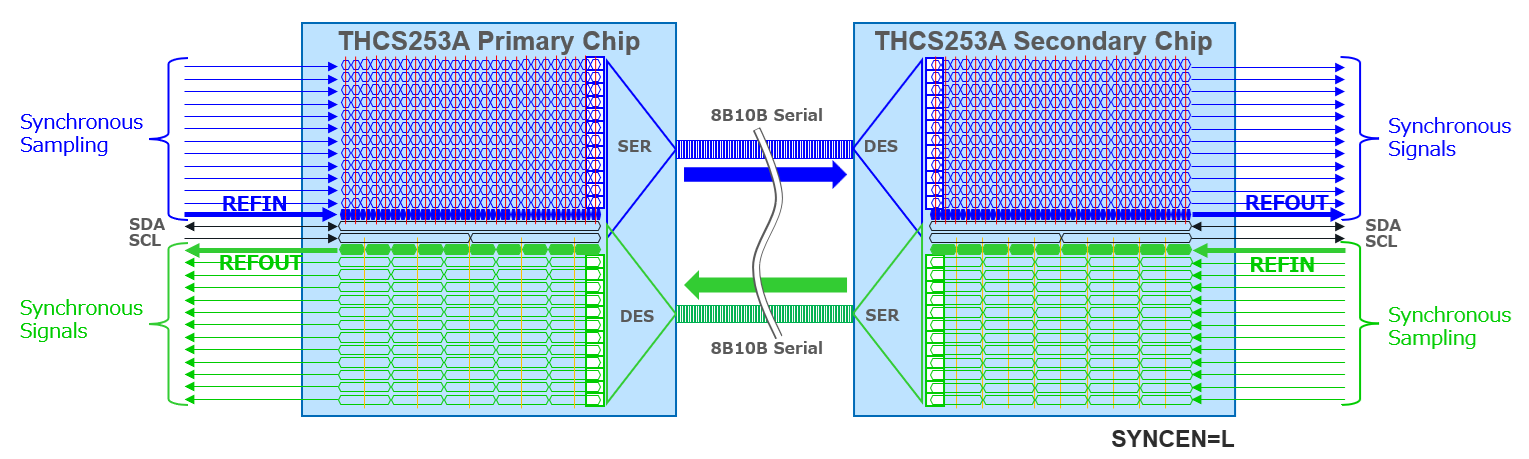

同期モードとは、プライマリ・チップからセカンダリ・チップへのダウンリンク(下り)と、セカンダリ・チップからプライマリ・チップへのアップリンク(上り)が同じ基準クロック信号で動作する場合である。言い換えれば、ダウンリンクとアップリンクの基準クロック信号の周波数と位相がまったく同じケースである。実際には、プライマリ・チップから送られてきたシリアル信号(クロック信号を埋め込んだ8B10B変調信号)を受信し、セカンダリ・チップのクロック・データ・リカバリ(CDR:Clock Data Recovery)回路で抽出したクロック信号を使ってアップリンクを動かすケースが同期モードになる(図3、図4)。

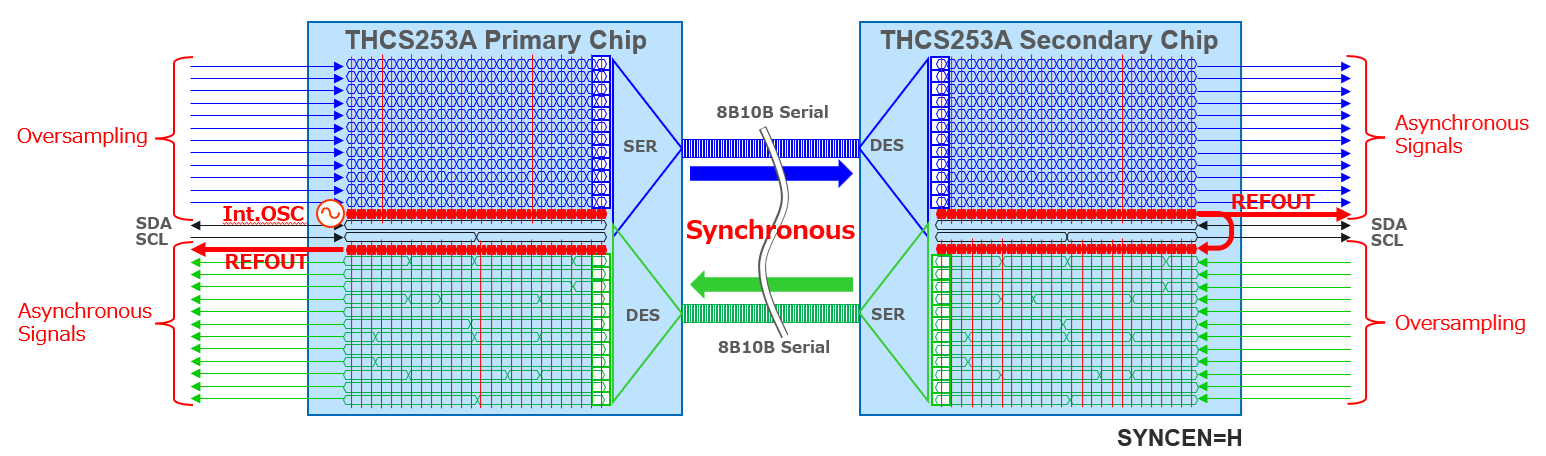

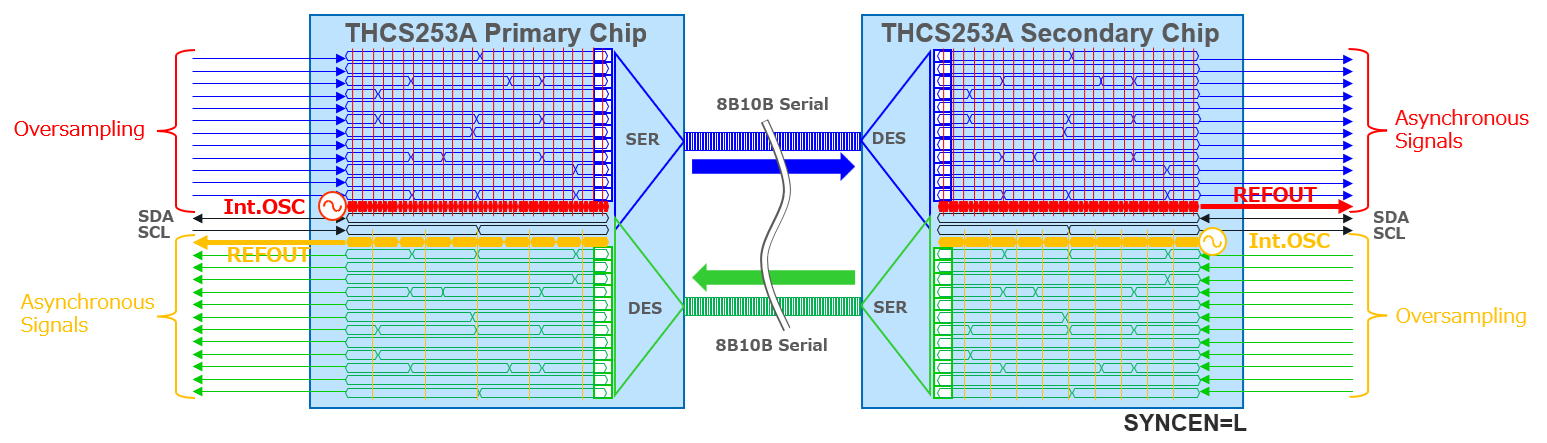

一方の非同期モードは、ダウンリンクとアップリンクがそれぞれ異なる基準クロック信号で動作する場合である(図5、図6)。仮に、両者の基準クロック信号の周波数が同じだとしても、位相が異なれば非同期モードになる。

同期モードのメリットとしては、セカンダリ・チップに供給する基準クロック信号源が不要なことが挙げられる。ただし、デメリットもある。それはプライマリ・チップでしか、パラレル信号の同期取り込みを実現できないことだ。セカンダリ・チップについては、使用する基準クロック信号はCDR回路で抽出したものであり取り込むパラレル信号と無関係なため、非同期取り込みとなる。同期取り込みが可能なダウンリンクは高速な画像/映像信号を伝送できるが、非同期取り込みのアップリンクは高速な画像/映像信号は送れず、低速の制御信号の伝送にしか使えない。

このデメリットの解消を狙って導入したのが非同期モードである。プライマリ・チップとセカンダリ・チップの両方で、別々の基準クロック信号を供給できるようにしたため、両方でパラレル信号の同期取り込みが可能になる。つまり、ダウンリンクとアップリンクともに、高速な画像/映像信号を送れるようになるわけだ。

しかし、ここで注意してほしい点が1つある。それはプライマリ・チップとセカンダリ・チップに基準クロック信号を供給する方法である。供給方法は2つある。1つは、外部のクロック信号回路から供給する方法。もう1つは、各チップに内蔵したクロック発振回路(内部OSC)から供給する方法である。前者は、パラレル信号の基準クロック信号と共用することで同期取り込みが可能になる。しかし後者は、内部OSCのクロック信号を外部に出力できないため、パラレル信号の基準クロック信号とは共用できず、非同期取り込みになってしまう。従って、ユーザーはダウンリンクとアップリンクで伝送したい信号の特性に合わせて、基準クロック信号の供給方法を選ぶ必要がある。

同期モードとは、プライマリ・チップからセカンダリ・チップへのダウンリンク(下り)と、セカンダリ・チップからプライマリ・チップへのアップリンク(上り)が同じ基準クロック信号で動作する場合である。言い換えれば、ダウンリンクとアップリンクの基準クロック信号の周波数と位相がまったく同じケースである。実際には、プライマリ・チップから送られてきたシリアル信号(クロック信号を埋め込んだ8B10B変調信号)を受信し、セカンダリ・チップのクロック・データ・リカバリ(CDR:Clock Data Recovery)回路で抽出したクロック信号を使ってアップリンクを動かすケースが同期モードになる(図3、図4)。

図3 同期モードの例(外部入力の場合)

図4 同期モードの例(内部OSCの場合)

一方の非同期モードは、ダウンリンクとアップリンクがそれぞれ異なる基準クロック信号で動作する場合である(図5、図6)。仮に、両者の基準クロック信号の周波数が同じだとしても、位相が異なれば非同期モードになる。

図5 非同期モードの例(外部入力の場合)

図6 非同期モードの例(内部OSCの場合)

同期モードのメリットとしては、セカンダリ・チップに供給する基準クロック信号源が不要なことが挙げられる。ただし、デメリットもある。それはプライマリ・チップでしか、パラレル信号の同期取り込みを実現できないことだ。セカンダリ・チップについては、使用する基準クロック信号はCDR回路で抽出したものであり取り込むパラレル信号と無関係なため、非同期取り込みとなる。同期取り込みが可能なダウンリンクは高速な画像/映像信号を伝送できるが、非同期取り込みのアップリンクは高速な画像/映像信号は送れず、低速の制御信号の伝送にしか使えない。

このデメリットの解消を狙って導入したのが非同期モードである。プライマリ・チップとセカンダリ・チップの両方で、別々の基準クロック信号を供給できるようにしたため、両方でパラレル信号の同期取り込みが可能になる。つまり、ダウンリンクとアップリンクともに、高速な画像/映像信号を送れるようになるわけだ。

しかし、ここで注意してほしい点が1つある。それはプライマリ・チップとセカンダリ・チップに基準クロック信号を供給する方法である。供給方法は2つある。1つは、外部のクロック信号回路から供給する方法。もう1つは、各チップに内蔵したクロック発振回路(内部OSC)から供給する方法である。前者は、パラレル信号の基準クロック信号と共用することで同期取り込みが可能になる。しかし後者は、内部OSCのクロック信号を外部に出力できないため、パラレル信号の基準クロック信号とは共用できず、非同期取り込みになってしまう。従って、ユーザーはダウンリンクとアップリンクで伝送したい信号の特性に合わせて、基準クロック信号の供給方法を選ぶ必要がある。

スタンバイ機能の使い勝手を高める

最後に、後継品で新たに対応したI2Cを使って実現した便利な新機能を3つ紹介する。

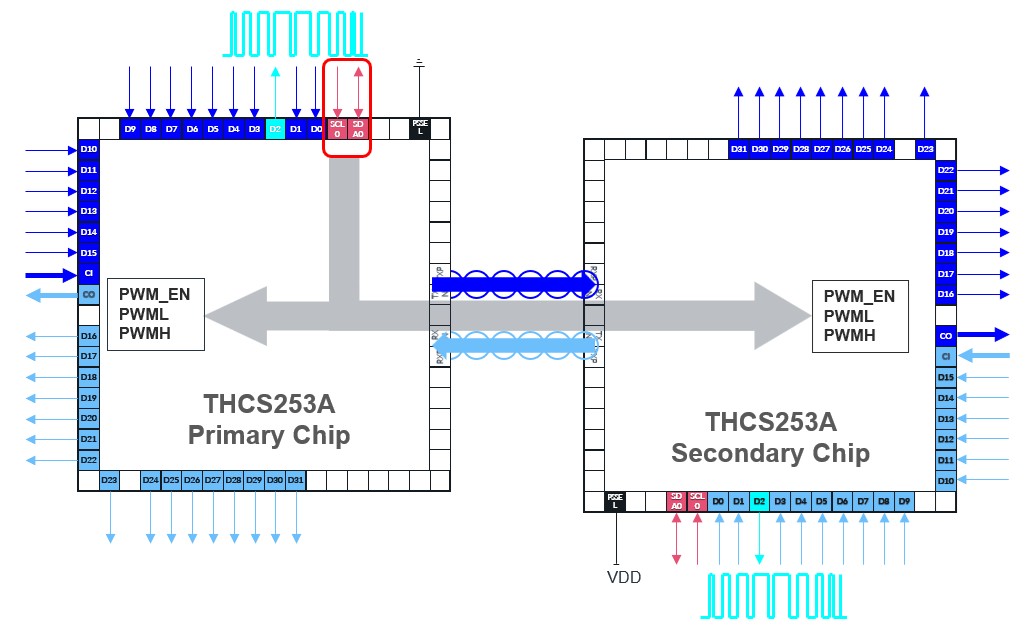

1つ目は、「PWM信号生成機能」である(図7)。従来品では、プライマリ・チップのGPIOで非同期取り込みが可能な周波数のPWM信号を入力し、それをシリアル信号に束ねてセカンダリ・チップに送ることは可能だった。しかし、後継品では、I2C 経由で内部レジスタを設定することでPWM信号を生成する機能を搭載した。プライマリ・チップでも、セカンダリ・チップでも生成できる。液晶パネルのバックライトの輝度調整や、LEDの調光、モーターの駆動などに使える。

2つ目は、「I/Oエキスパンダ機能」である(図8)。この機能は、I2CとGPIOの間でデータを変換し、それをプライマリ・チップもしくはセカンダリ・チップに送るというもの。I2Cのシリアル・データをGPOのパラレル・データに変換して送ったり、GPIに入力されたパラレル・データをモニターし、その結果を内部レジスタに格納してI2Cからシリアル・データとして出力したりすることができる。あたかもI2C端子を拡張したように見えるため、I/Oエキスパンダ機能と呼ぶ。

3つ目は、「スタンバイ機能」である(図9)。今回の後継品では、I2Cを介して内部レジスタを書き換えることでスタンバイ状態に移行、もしくは離脱できるようにした。プライマリ・チップ側から、プライマリ・チップのスタンバイ状態への移行/離脱はもちろんのこと、セカンダリ・チップの移行/離脱も設定可能だ。

スタンバイ状態での消費電流は6mAと少ない。通常動作時は50~100mAである。スタンバイ状態でも、I2Cや最大8ビットのGPIOをプライマリ・チップとセカンダリ・チップの間でやり取りできる。さらにスタンバイ状態でも、光電変換デバイスを介した光伝送や、近距離無線通信デバイスを介した無線伝送を継続可能だ。従って、リンクを切ることなくノーマル動作の状態からスタンバイ状態に切り替えられる。

以上

1つ目は、「PWM信号生成機能」である(図7)。従来品では、プライマリ・チップのGPIOで非同期取り込みが可能な周波数のPWM信号を入力し、それをシリアル信号に束ねてセカンダリ・チップに送ることは可能だった。しかし、後継品では、I2C 経由で内部レジスタを設定することでPWM信号を生成する機能を搭載した。プライマリ・チップでも、セカンダリ・チップでも生成できる。液晶パネルのバックライトの輝度調整や、LEDの調光、モーターの駆動などに使える。

図7 PWM信号生成機能

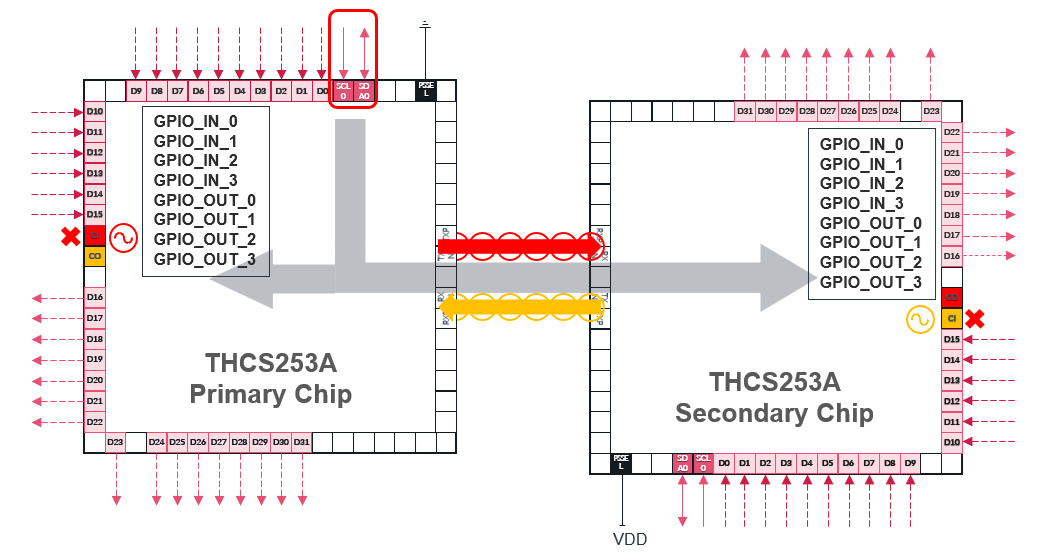

2つ目は、「I/Oエキスパンダ機能」である(図8)。この機能は、I2CとGPIOの間でデータを変換し、それをプライマリ・チップもしくはセカンダリ・チップに送るというもの。I2Cのシリアル・データをGPOのパラレル・データに変換して送ったり、GPIに入力されたパラレル・データをモニターし、その結果を内部レジスタに格納してI2Cからシリアル・データとして出力したりすることができる。あたかもI2C端子を拡張したように見えるため、I/Oエキスパンダ機能と呼ぶ。

図8 I/Oエキスパンダ機能

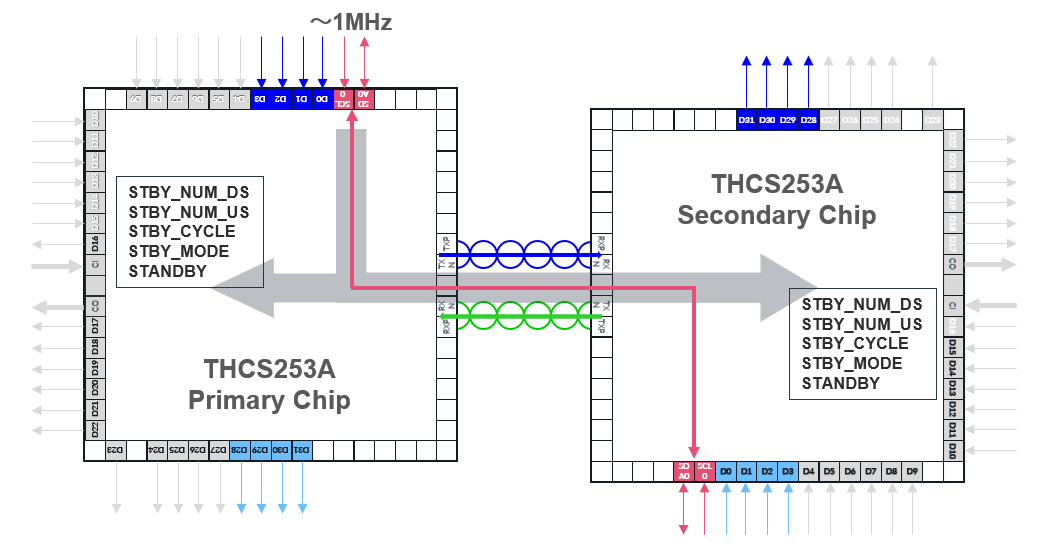

3つ目は、「スタンバイ機能」である(図9)。今回の後継品では、I2Cを介して内部レジスタを書き換えることでスタンバイ状態に移行、もしくは離脱できるようにした。プライマリ・チップ側から、プライマリ・チップのスタンバイ状態への移行/離脱はもちろんのこと、セカンダリ・チップの移行/離脱も設定可能だ。

図9 スタンバイ機能

スタンバイ状態での消費電流は6mAと少ない。通常動作時は50~100mAである。スタンバイ状態でも、I2Cや最大8ビットのGPIOをプライマリ・チップとセカンダリ・チップの間でやり取りできる。さらにスタンバイ状態でも、光電変換デバイスを介した光伝送や、近距離無線通信デバイスを介した無線伝送を継続可能だ。従って、リンクを切ることなくノーマル動作の状態からスタンバイ状態に切り替えられる。

以上