THine Value FPGAを使わずともI/O問題をシンプルに解決!GPIOとI2Cを束ねて送るシリアル・トランシーバ

2025.09.29

- 記事

- コラム

現在、産業機器市場におけるFA機器、オフィス機器、セキュリティ/監視機器、輸送機器などの電子機器では、カメラモジュールや各種センサーの搭載数が増加する傾向にある。その背景にあるのは、カメラモジュールの低価格化や使い勝手の向上、IoT(Internet of Things)への取り組み強化などだ。もちろん、カメラモジュールや各種センサーを数多く搭載すれば、上記のような電子機器の機能や性能を飛躍的に向上させたり、使い勝手を大幅に高めたりできるだろう。得られるメリットは極めて大きい。

しかしその一方で、設計の難易度が高まるという問題に遭遇する。例えば、「生産ラインが長いため、その全体をカメラで監視しようとすると映像データの伝送距離が足りない」「各種センサーで取得したデータを送るケーブルの本数が多すぎて、電子機器本体の重量が増えてしまう」「離れた場所をカメラで監視するため、映像データの伝送距離を1km程度に延ばしたい」「産業機器の設置環境が劣悪なため、センサーとつなぐ高速伝送路を防塵対応にしたり、容易に着脱できるようにしたい」などである。こうした問題を解決しつつ、カメラモジュールや各種センサーを必要に応じて採用して電子機器の機能や性能、使い勝手を向上させる。これが産業機器の開発者が現在抱えている課題だ。

しかしその一方で、設計の難易度が高まるという問題に遭遇する。例えば、「生産ラインが長いため、その全体をカメラで監視しようとすると映像データの伝送距離が足りない」「各種センサーで取得したデータを送るケーブルの本数が多すぎて、電子機器本体の重量が増えてしまう」「離れた場所をカメラで監視するため、映像データの伝送距離を1km程度に延ばしたい」「産業機器の設置環境が劣悪なため、センサーとつなぐ高速伝送路を防塵対応にしたり、容易に着脱できるようにしたい」などである。こうした問題を解決しつつ、カメラモジュールや各種センサーを必要に応じて採用して電子機器の機能や性能、使い勝手を向上させる。これが産業機器の開発者が現在抱えている課題だ。

パラレル伝送をシリアル伝送に置き換える

こうした課題を解決することを目的に、ザインエレクトロニクスは新しいシリアル・トランシーバIC「THCS253A/THCS254A」をリリースしている。製品のニックネームは「IOHA:B」(アイオーハブと発音)だ。

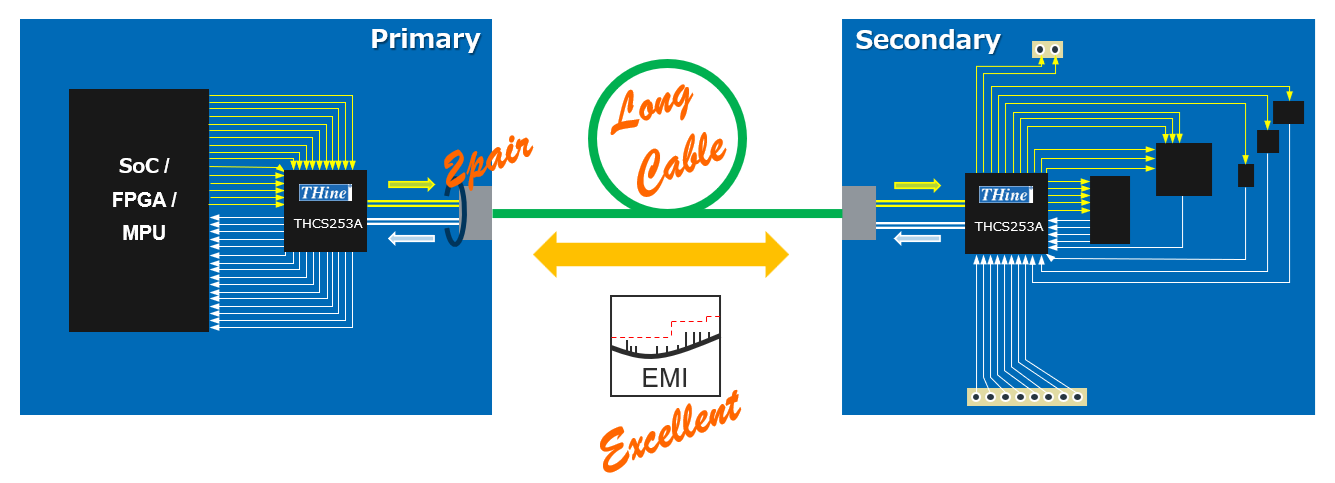

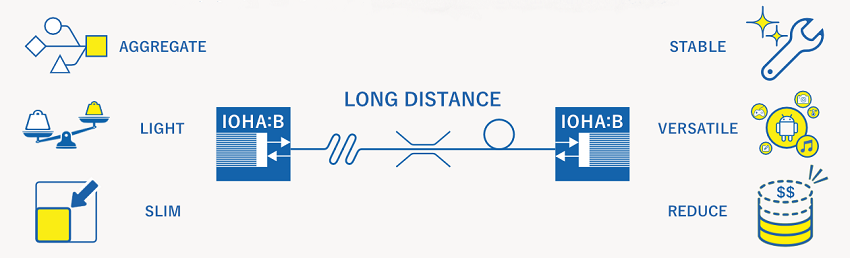

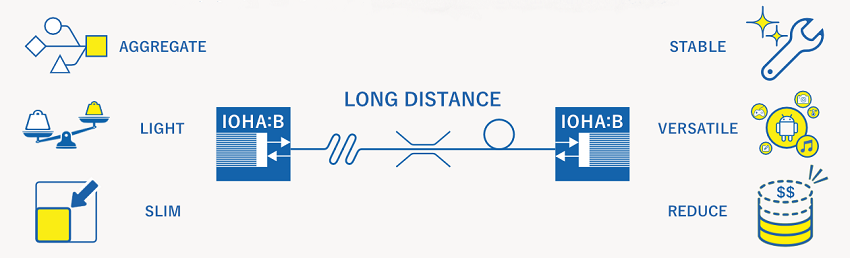

本製品はトランスミッタ(送信回路、シリアライザ)とレシーバ(受信回路、デシリアライザ)を1チップに集積したもの。このためSerDesトランシーバICとも呼ばれる。製品を2つ用意して、一方をプライマリ・チップに、もう一方をセカンダリ・チップに端子設定して使用する。これらの間は、2ペアの差動ラインで接続し、一方をアップリンク(上り)、もう一方をダウンリンク(下り)とする。つまり、上りと下りの信号ラインをそれぞれ別々に設けることで送受を同時に行う全二重通信方式を実現できる。数多くの信号ラインからなるパラレル伝送を、わずか2ペアの差動ラインによるシリアル伝送に置き換えるといった使い方を想定する(図1)。

具体的なアプリケーションは、電子機器の機器間や、その内部のボード間におけるデータ伝送である。機器間やボード間を接続する30本を超える数多くの信号ラインをたった2ペアの差動ライン(4本の信号ライン)に束ねられるため、配線ケーブルの本数の削減や総重量の削減に加えて、伝送距離の延長などを実現できる。つまり冒頭で紹介した課題をいずれも解決できるわけだ。

実はザインエレクトロニクスはすでに、ほぼ同じ使い方ができるシリアル・トランシーバICの従来品「THCS251/THCS252」を2019年末に製品化していた。THCS253A/THCS254Aは、従来品の後継版に当たる。後継品では、従来品が持っていた基本機能をそのまま継承しながら、新たに大きな変更を加えた。その変更は、束ねられる信号ラインとして複数本のGPIO(汎用入出力)に加えて、1系統もしくは2系統のI2Cを追加したことだ。THCS253AはGPIOを最大32本、THCS254Aは最大20本を用意しており、両製品とも1系統のI2Cをデフォルトで搭載している。さらにユーザーが所定の設定を行えば、2本のGPIOをI2Cに割り当てられる。つまり最大で2系統のI2CをGPIOとともに束ねてシリアル伝送できることになる。

本製品はトランスミッタ(送信回路、シリアライザ)とレシーバ(受信回路、デシリアライザ)を1チップに集積したもの。このためSerDesトランシーバICとも呼ばれる。製品を2つ用意して、一方をプライマリ・チップに、もう一方をセカンダリ・チップに端子設定して使用する。これらの間は、2ペアの差動ラインで接続し、一方をアップリンク(上り)、もう一方をダウンリンク(下り)とする。つまり、上りと下りの信号ラインをそれぞれ別々に設けることで送受を同時に行う全二重通信方式を実現できる。数多くの信号ラインからなるパラレル伝送を、わずか2ペアの差動ラインによるシリアル伝送に置き換えるといった使い方を想定する(図1)。

図1 パラレル伝送をシリアル伝送に置き換える

具体的なアプリケーションは、電子機器の機器間や、その内部のボード間におけるデータ伝送である。機器間やボード間を接続する30本を超える数多くの信号ラインをたった2ペアの差動ライン(4本の信号ライン)に束ねられるため、配線ケーブルの本数の削減や総重量の削減に加えて、伝送距離の延長などを実現できる。つまり冒頭で紹介した課題をいずれも解決できるわけだ。

実はザインエレクトロニクスはすでに、ほぼ同じ使い方ができるシリアル・トランシーバICの従来品「THCS251/THCS252」を2019年末に製品化していた。THCS253A/THCS254Aは、従来品の後継版に当たる。後継品では、従来品が持っていた基本機能をそのまま継承しながら、新たに大きな変更を加えた。その変更は、束ねられる信号ラインとして複数本のGPIO(汎用入出力)に加えて、1系統もしくは2系統のI2Cを追加したことだ。THCS253AはGPIOを最大32本、THCS254Aは最大20本を用意しており、両製品とも1系統のI2Cをデフォルトで搭載している。さらにユーザーが所定の設定を行えば、2本のGPIOをI2Cに割り当てられる。つまり最大で2系統のI2CをGPIOとともに束ねてシリアル伝送できることになる。

光化/無線化にも容易に対応

今回の後継品は、従来品のTHCS251/THCS252が持つメリットはそのままに、新たなメリットをユーザーに提供できる。まずは従来品から継承したメリットを確認しておく。メリットは大きく6つある。

1つ目は、パラレル伝送をシリアル伝送に置き換えられるため、配線ケーブルの本数を削減できることだ。例えば、THCS253Aであれば、34本(32本のGPIO+1系統のI2C)の信号ラインをわずか差動2ペア(4本)に減らせる。つまり配線ケーブルの本数は最大88%削減できる計算になる。この結果、34本の配線ケーブルを通せなかった狭い隙間でも通せるようになる。例えば、インクジェック・プリンタなどの電子機器のコンパクト化に貢献する。

2つ目は、配線ケーブルの総重量を減らせることである。配線ケーブルの本数を大幅に削減できるからだ。この効果は大きい。例えば、ドローン本体を軽量化できるので、電池駆動時間を延ばせるようになり、より長い時間の飛行が可能になる。

3つ目は、配線ケーブルの接続作業を簡略化できることだ。接続する必要があるケーブルの本数が減るからである。この結果、配線ミスを減らせたり、作業効率の向上を図ったりすることができる。

4つ目は、信号品質(シグナル・インテグリティ)を維持したまま、伝送距離を延ばせることである。パラレル伝送では、クロック周波数が100MHzの場合に伝送可能な距離はせいぜい1mである。一方、シリアル伝送については、送られてきた信号の周波数特性を補償して波形整形する連続時間リニア・イコライザ(CTLE:Continues Time Linear Equalizer)を受信回路に搭載したため、伝送距離は使用する配線ケーブルの品質に依存するが、クロック周波数が100MHzの場合(伝送速度は3.0Gビット/秒)に約10mまで延ばせる。

5つ目は、電磁ノイズ(EMI:Electro-Magnetic Interference)の放射レベルを抑えられること。理由は2つある。1つは、クロック信号埋め込み型のSerDes回路を採用していること。もう1つは、伝送媒体が2本の信号ラインで構成する差動ケーブルであるためだ。それぞれの信号ラインから放射されるノイズは相殺される。

6つ目は、設計の共通化が可能であることだ。従来品のTHCS251は、GPIOを最大35本用意しているが、これをすべて使い切るユースケースはほとんどない。余った端子(空き端子)が発生する。これを有効活用することで設計を共通化できる。例えば、余った端子を使って、あらかじめマイコン/FPGAとコネクタの間を接続しておく。こうしておけば複数の機種で機能が若干異なっても、信号伝送路などのハードウエア設計はそのままに、余った端子に新しい信号をアサインするだけで機能の違いを吸収できた。しかも従来品のTHCS251/THCS252は、汎用入力(GPI)と汎用出力(GPO)の本数の比率を4段階で設定できる機能を備えている。これを使えば、機能の違いを吸収できる範囲を広げられる。つまり、1つのハードウエア設計だけで複数の機種を実現する設計の共通化が可能だったわけだ。

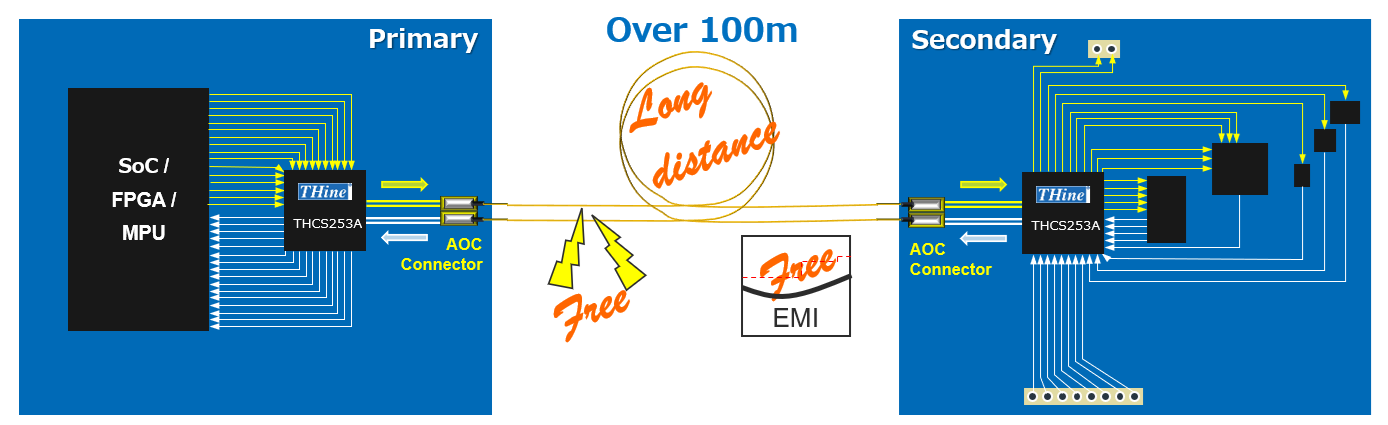

これらのメリット以外にも、大きな特徴がもう1つある。それは、光化と無線化が簡単なことだ。前述の通り、後継品はダウンリンク(下り)とアップリンク(上り)の伝送路をそれぞれ用意した全二重通信方式を採用している。従って、それぞれに光電変換デバイス、もしくは近距離無線通信デバイス(ミリ波通信デバイス)を接続するだけで、機器間やボード間の接続を光化、もしくは無線化できる。この結果、応用範囲は大きく広がる。光化すれば、2つの電子機器の距離が数10~数100mと大きく離れている用途や、ノイズ環境が劣悪な用途、電気的な絶縁が求められる用途でも適用できるようになる(図2)。

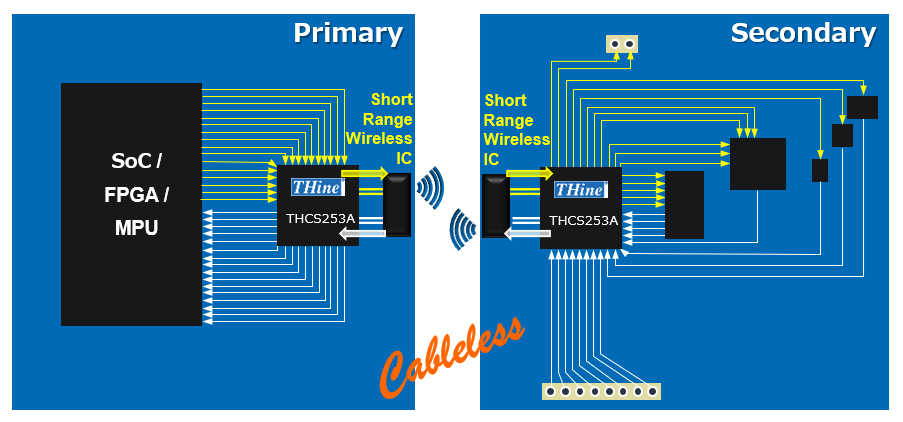

一方、無線化を採用すれば、工場などにおいて防塵が求められる用途や、電気的な絶縁が求められる用途に使えるようになる(図3)。

1つ目は、パラレル伝送をシリアル伝送に置き換えられるため、配線ケーブルの本数を削減できることだ。例えば、THCS253Aであれば、34本(32本のGPIO+1系統のI2C)の信号ラインをわずか差動2ペア(4本)に減らせる。つまり配線ケーブルの本数は最大88%削減できる計算になる。この結果、34本の配線ケーブルを通せなかった狭い隙間でも通せるようになる。例えば、インクジェック・プリンタなどの電子機器のコンパクト化に貢献する。

2つ目は、配線ケーブルの総重量を減らせることである。配線ケーブルの本数を大幅に削減できるからだ。この効果は大きい。例えば、ドローン本体を軽量化できるので、電池駆動時間を延ばせるようになり、より長い時間の飛行が可能になる。

3つ目は、配線ケーブルの接続作業を簡略化できることだ。接続する必要があるケーブルの本数が減るからである。この結果、配線ミスを減らせたり、作業効率の向上を図ったりすることができる。

4つ目は、信号品質(シグナル・インテグリティ)を維持したまま、伝送距離を延ばせることである。パラレル伝送では、クロック周波数が100MHzの場合に伝送可能な距離はせいぜい1mである。一方、シリアル伝送については、送られてきた信号の周波数特性を補償して波形整形する連続時間リニア・イコライザ(CTLE:Continues Time Linear Equalizer)を受信回路に搭載したため、伝送距離は使用する配線ケーブルの品質に依存するが、クロック周波数が100MHzの場合(伝送速度は3.0Gビット/秒)に約10mまで延ばせる。

5つ目は、電磁ノイズ(EMI:Electro-Magnetic Interference)の放射レベルを抑えられること。理由は2つある。1つは、クロック信号埋め込み型のSerDes回路を採用していること。もう1つは、伝送媒体が2本の信号ラインで構成する差動ケーブルであるためだ。それぞれの信号ラインから放射されるノイズは相殺される。

6つ目は、設計の共通化が可能であることだ。従来品のTHCS251は、GPIOを最大35本用意しているが、これをすべて使い切るユースケースはほとんどない。余った端子(空き端子)が発生する。これを有効活用することで設計を共通化できる。例えば、余った端子を使って、あらかじめマイコン/FPGAとコネクタの間を接続しておく。こうしておけば複数の機種で機能が若干異なっても、信号伝送路などのハードウエア設計はそのままに、余った端子に新しい信号をアサインするだけで機能の違いを吸収できた。しかも従来品のTHCS251/THCS252は、汎用入力(GPI)と汎用出力(GPO)の本数の比率を4段階で設定できる機能を備えている。これを使えば、機能の違いを吸収できる範囲を広げられる。つまり、1つのハードウエア設計だけで複数の機種を実現する設計の共通化が可能だったわけだ。

これらのメリット以外にも、大きな特徴がもう1つある。それは、光化と無線化が簡単なことだ。前述の通り、後継品はダウンリンク(下り)とアップリンク(上り)の伝送路をそれぞれ用意した全二重通信方式を採用している。従って、それぞれに光電変換デバイス、もしくは近距離無線通信デバイス(ミリ波通信デバイス)を接続するだけで、機器間やボード間の接続を光化、もしくは無線化できる。この結果、応用範囲は大きく広がる。光化すれば、2つの電子機器の距離が数10~数100mと大きく離れている用途や、ノイズ環境が劣悪な用途、電気的な絶縁が求められる用途でも適用できるようになる(図2)。

図2 光化が容易に

一方、無線化を採用すれば、工場などにおいて防塵が求められる用途や、電気的な絶縁が求められる用途に使えるようになる(図3)。

図3 無線化が容易に

急な機能追加でもハードの再設計は不要

このようにザインエレクトロニクスのシリアル・トランシーバICは、従来品でも上記のような複数のメリットを享受できる。これに加えて後継品のTHCS253A/THCS254Aは、I2Cへの対応でI/O(入出力インターフェース)部の設計自由度を大幅に高められるというメリットがある。

一般に電子機器の開発現場では、設計に着手した後に急遽、設計内容を変更されることが決して少なくない。例えば、新しい機能の追加などである。この場合は追加される機能にもよるが、サブボードなどとやり取りする信号ラインが増えてしまい、信号伝送路などのハードウエア設計の変更を強いられることがある。もちろん再設計に取り組むことになれば、それに費やす工数や期間、コストが増えてしまう。

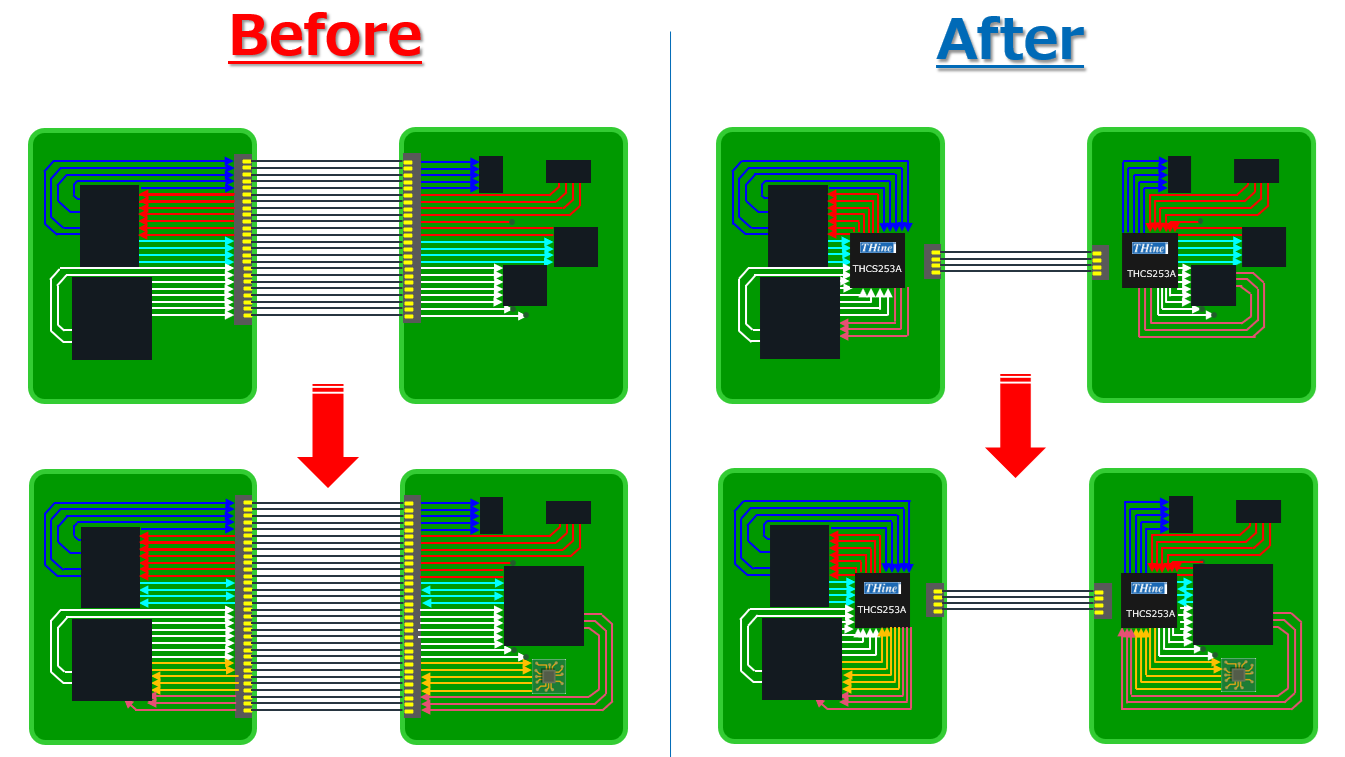

できれば、急な設計変更が発生しても、ハードウエアの再設計は避けたいところだ。こうした場合に、今回の後継品は大きな効果を発揮する。なぜならば、I2Cに対応しているため、これを介して内部レジスタにアクセスしてデータを書き換えることで1端子ごとに自由にカスタマイズできるからだ。つまり信号伝送路などのハードウエア設計はそのままに、内部レジスタを書き換えるだけで機能追加などに極めて柔軟に対応できることになる(図4)。

従来品のTHCS251/THCS252も、前述のようにGPIとGPOの本数比率を4段階で設定できる機能を搭載しており、これを活用すれば、急な設計変更にある程度対応することが可能だった。しかし、カスタマイズできる範囲はTHCS253A/THCS254Aの方が圧倒的に広い。このため後継品を使えば、従来品に比べて設計変更時にハードウエアの再設計が発生する確率を大幅に下げられる。

それでは今回の後継品が登場する前は、ハードウエア再設計の発生を防げる有効な対処法は存在しなかったのか。もちろん、FPGAを使えば実現できた。しかし、大きなデメリットがあった。それは、FPGA内部の回路設計やプリント基板のレイアウト設計などの作業が発生して設計の手間が増えることだ。加えて、コストも増えてしまう。そもそも設計に着手した後に機能追加などの変更の可能性があるという理由だけで、I/O部にあらかじめFPGAを導入しておくという判断を下すのは難しいと言えるだろう。

しかしTHCS253A/THCS254Aは、I2Cを介してカスタマイズする回路を1チップに集積したため、FPGAとは異なり導入時の設計の手間が増えることはほぼない。機能追加が発生した場合は内蔵レジスタの書き換えだけで対処できるため、信号伝送路などのハードウエアの再設計は一切不要にできる。

本稿(前編)では、後継品のTHCS253A/THCS254Aにおいて従来品から変更された点、すなわちGPIOに加えてI2Cに対応したことを解説し、そのメリットとして高い自由度でI/O部をカスタマイズできるようにしたことを紹介した(図5)。

本記事の後編では、この変更点をより詳しく説明することに加えて、もう1つの変更点である「同期/非同期モードの導入」を解説する。

以上

一般に電子機器の開発現場では、設計に着手した後に急遽、設計内容を変更されることが決して少なくない。例えば、新しい機能の追加などである。この場合は追加される機能にもよるが、サブボードなどとやり取りする信号ラインが増えてしまい、信号伝送路などのハードウエア設計の変更を強いられることがある。もちろん再設計に取り組むことになれば、それに費やす工数や期間、コストが増えてしまう。

できれば、急な設計変更が発生しても、ハードウエアの再設計は避けたいところだ。こうした場合に、今回の後継品は大きな効果を発揮する。なぜならば、I2Cに対応しているため、これを介して内部レジスタにアクセスしてデータを書き換えることで1端子ごとに自由にカスタマイズできるからだ。つまり信号伝送路などのハードウエア設計はそのままに、内部レジスタを書き換えるだけで機能追加などに極めて柔軟に対応できることになる(図4)。

図4 ハードウエア設計の柔軟性が向上

従来品のTHCS251/THCS252も、前述のようにGPIとGPOの本数比率を4段階で設定できる機能を搭載しており、これを活用すれば、急な設計変更にある程度対応することが可能だった。しかし、カスタマイズできる範囲はTHCS253A/THCS254Aの方が圧倒的に広い。このため後継品を使えば、従来品に比べて設計変更時にハードウエアの再設計が発生する確率を大幅に下げられる。

それでは今回の後継品が登場する前は、ハードウエア再設計の発生を防げる有効な対処法は存在しなかったのか。もちろん、FPGAを使えば実現できた。しかし、大きなデメリットがあった。それは、FPGA内部の回路設計やプリント基板のレイアウト設計などの作業が発生して設計の手間が増えることだ。加えて、コストも増えてしまう。そもそも設計に着手した後に機能追加などの変更の可能性があるという理由だけで、I/O部にあらかじめFPGAを導入しておくという判断を下すのは難しいと言えるだろう。

しかしTHCS253A/THCS254Aは、I2Cを介してカスタマイズする回路を1チップに集積したため、FPGAとは異なり導入時の設計の手間が増えることはほぼない。機能追加が発生した場合は内蔵レジスタの書き換えだけで対処できるため、信号伝送路などのハードウエアの再設計は一切不要にできる。

本稿(前編)では、後継品のTHCS253A/THCS254Aにおいて従来品から変更された点、すなわちGPIOに加えてI2Cに対応したことを解説し、そのメリットとして高い自由度でI/O部をカスタマイズできるようにしたことを紹介した(図5)。

図5 IOHA:B(THCSシリーズ)の特長

本記事の後編では、この変更点をより詳しく説明することに加えて、もう1つの変更点である「同期/非同期モードの導入」を解説する。

以上