THine Value 高速伝送時代のESD保護

2023.02.07

- 記事

- コラム

近年ICレベルではプロセスの微細化が進み、ESD耐性が下がる傾向にある。一方でパッケージレベルではI/Oピン数が増え、外部からのESDによる影響が増えてきている。

そのためコネクタから侵入する静電気からICデバイスの破壊を防ぐ対策を講じる必要がある。そのキーパーツとなるのがTVS(Transient Voltage Suppressors)だ。

ではTVSを置くときのポイントは何か。特にケアが必要なのは高速信号ラインだ。高速ラインはESD保護ダイオードを減らす事で低容量化し、信号劣化につながるインサーションロスを低減させているが、その副作用としてESD耐性が下がってしまう。

どうすれば高速信号伝送時にESDによるICデバイス破壊を回避できるか。本コラムでは、高速信号ラインで使用されるTVSについて考察する。

そのためコネクタから侵入する静電気からICデバイスの破壊を防ぐ対策を講じる必要がある。そのキーパーツとなるのがTVS(Transient Voltage Suppressors)だ。

ではTVSを置くときのポイントは何か。特にケアが必要なのは高速信号ラインだ。高速ラインはESD保護ダイオードを減らす事で低容量化し、信号劣化につながるインサーションロスを低減させているが、その副作用としてESD耐性が下がってしまう。

どうすれば高速信号伝送時にESDによるICデバイス破壊を回避できるか。本コラムでは、高速信号ラインで使用されるTVSについて考察する。

進むプロセスの微細化

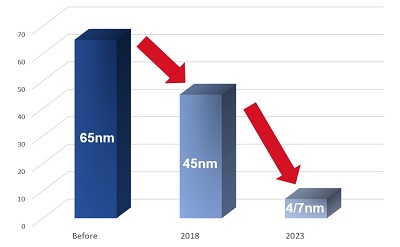

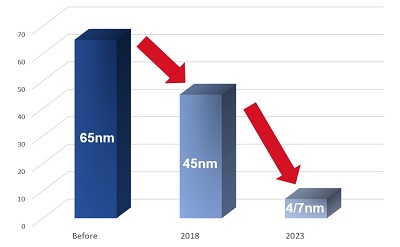

近年、AI機能を搭載したシステムやIoTテクノロジーが社会に浸透していくに従い、処理しなければならないデータ量が膨大になっており、その要となるFPGAやSoC、ASIC、マイコンなどシステムLSIの高集積化が加速している。高集積化には微細プロセスが必要だが、信号の入出力部におけるESD耐圧の低下が顕著となっている。

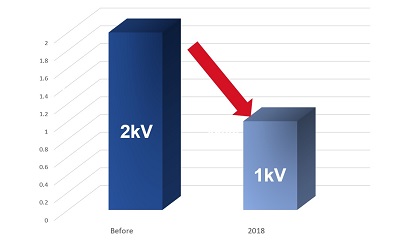

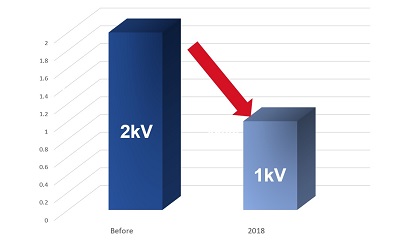

プロセス微細化が進んでいるのに呼応するかのように、2018年7月、JEDECはJEP155B「Recommended ESD Target Level for HBM Qualification」の10.1項にて、ICデバイスに要求されるHBMの値としてこれまでの2kVから1kVに耐圧を下げた値を適切値として推奨している。つまりは、これまでよりもより弱いESDでもICデバイスを壊す可能性があるということだ。今後HBMが1kVのICデバイスが増えていくに従い、システムレベルで保護する対策が必要となり、TVSの重要性が高まってきていると言える。

図1 高集積LSIのプロセスノードの変遷

プロセス微細化が進んでいるのに呼応するかのように、2018年7月、JEDECはJEP155B「Recommended ESD Target Level for HBM Qualification」の10.1項にて、ICデバイスに要求されるHBMの値としてこれまでの2kVから1kVに耐圧を下げた値を適切値として推奨している。つまりは、これまでよりもより弱いESDでもICデバイスを壊す可能性があるということだ。今後HBMが1kVのICデバイスが増えていくに従い、システムレベルで保護する対策が必要となり、TVSの重要性が高まってきていると言える。

図2 ICデバイスに対する推奨HBMのESD耐圧

進む信号伝送速度の高速化

先の項で処理されるデータ量が増えてきたと述べた。例えばAI処理のために多様なアプリケーションで機器にカメラがつき映像データが送られるケースが増えてきたことや、動画がFull HDや4K2Kなどとなり高解像度化していることがその原因に挙げられる。

それに対応するため、様々な機器に高速信号伝送用のポートが搭載されており、そしてその速度は近年高速化する一方だ。例えばノートPCには40Gbpsの速度で通信できるThunderboltTM4のポートを持つ製品も増えてきている。その他、産業用PC等には16GbpsのPCIe Gen4、ゲーミング用途などに使われるディスプレイには48Gbpsの速度を持つHDMI 2.1も使われている。更に、パソコン本体とディスプレイを結ぶインターフェースにはDisplayPortもある。これも2019年に策定された最新規格DisplayPort 2.0において、32.4Gbpsに高められている。機器間通信で多く使われているUSBも着実に高速化が進んでおり、Display Port, USB3.2 Gen2x2では20Gbpsとなっている。

それに対応するため、様々な機器に高速信号伝送用のポートが搭載されており、そしてその速度は近年高速化する一方だ。例えばノートPCには40Gbpsの速度で通信できるThunderboltTM4のポートを持つ製品も増えてきている。その他、産業用PC等には16GbpsのPCIe Gen4、ゲーミング用途などに使われるディスプレイには48Gbpsの速度を持つHDMI 2.1も使われている。更に、パソコン本体とディスプレイを結ぶインターフェースにはDisplayPortもある。これも2019年に策定された最新規格DisplayPort 2.0において、32.4Gbpsに高められている。機器間通信で多く使われているUSBも着実に高速化が進んでおり、Display Port, USB3.2 Gen2x2では20Gbpsとなっている。

図3 高速信号伝送規格の例

高速信号伝送におけるESD保護の課題

そのような高速化が進むことで、データ伝送におけるインサーションロス(通過特性)の問題がクリティカルとなっている。インサーションロスとは、信号品質の指標だ。縦軸dB、横軸Hzで特定周波数での信号減衰を表すグラフを用いる。信号はその伝送線路上に抵抗成分が載っていると減衰が加速する。如何にインサーションロスを少なく抑えて信号の減衰を防ぐか、というのが最大の課題となる。

ESD保護の観点からは、伝送線路上にTVSを追加することは解決策のひとつであるが、TVSを載せることでそれが抵抗成分となってしまい、インサーションロスが増大、伝送線路が波状してしまうという課題がある。

ESD保護の観点からは、伝送線路上にTVSを追加することは解決策のひとつであるが、TVSを載せることでそれが抵抗成分となってしまい、インサーションロスが増大、伝送線路が波状してしまうという課題がある。

課題を解決できるザインエレクトロニクスのTVS

課題を解決する方法はある。それは容量(Cj)の小さいTVSを選択することだ。低容量のTVSはDCから高周波までのインサーションロスが小さく、デジタル信号品質を劣化を低く抑えることができる。

後述するダイナミック抵抗(Rdyn)と容量(Cj)を使いESD保護能力と波形への影響を表す係数(CjRd : ダイナミック抵抗 x 容量)を用いて、当社が今回新たにリリースしたTVS製品の性能を図4に示す。CjRd値が低いほどESDの保護能力に優れ、且つ、デジタル信号の波形に影響を与えにくい設計が可能となり、当社製品の性能が高い事が分かるだろう。

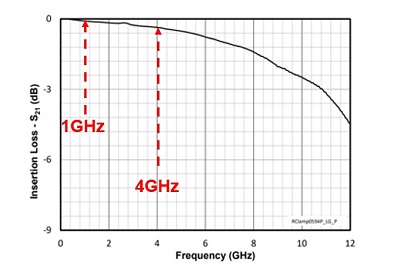

図5で示すのは、当社の4チャンネルTVS製品であるTHTVS514のインサーションロスグラフだ。1GHz(2Gbps)以下ではインサーションロスがほぼゼロ、4GHz(8Gbps)でもインサーションロスが-0.3dB以下と、ほぼ信号に影響を与えないレベルであることが見て頂けるだろう。当社TVSの他製品も、DCから高周波までフラットなロスの無い特性が特徴となっている。

後述するダイナミック抵抗(Rdyn)と容量(Cj)を使いESD保護能力と波形への影響を表す係数(CjRd : ダイナミック抵抗 x 容量)を用いて、当社が今回新たにリリースしたTVS製品の性能を図4に示す。CjRd値が低いほどESDの保護能力に優れ、且つ、デジタル信号の波形に影響を与えにくい設計が可能となり、当社製品の性能が高い事が分かるだろう。

図4 ダイナミック抵抗値(Rd) x 容量(Cj)の比較

図5で示すのは、当社の4チャンネルTVS製品であるTHTVS514のインサーションロスグラフだ。1GHz(2Gbps)以下ではインサーションロスがほぼゼロ、4GHz(8Gbps)でもインサーションロスが-0.3dB以下と、ほぼ信号に影響を与えないレベルであることが見て頂けるだろう。当社TVSの他製品も、DCから高周波までフラットなロスの無い特性が特徴となっている。

図5 THTVS514のインサーションロスグラフ(ライン-GND間)

それだけじゃない、ESD保護能力も備えるTVS

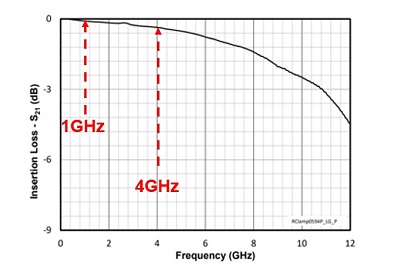

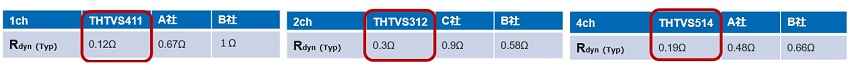

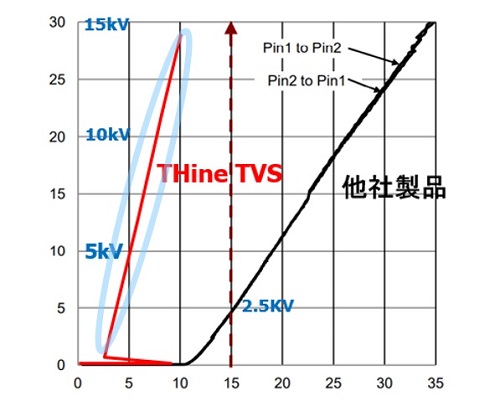

では、TVSはインサーションロスがフラットだけが良いことか。もちろん違う。TVSの最大の存在意義であるESD保護能力に優れていることが大切だ。前項に少し出たが、ダイナミック抵抗(Rdyn)も見るべきポイントとなる(図6)。

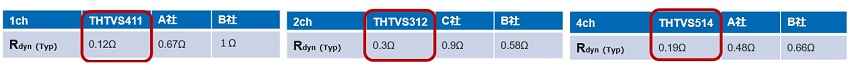

ダイナミック抵抗=TVS自身の抵抗成分が低いと、ESDを吸収しやすくなる。このダイナミック抵抗値が低いことで、図7で示す青丸枠の波形の傾きが緩やかになる。この傾きが緩くなると、破壊電圧に到達するまでの電流印可量(縦軸)が増える為、耐圧が上がる事になる。

ダイナミック抵抗の低いTVSでは、スナップバック特性には影響を与えることなくスナップバックした後の電圧上昇の傾きを緩くすることに寄与、すなわち、ICを保護する能力を向上させている。

図6 ダイナミック抵抗値(Rdyn)の比較(IEC-6100-4-2 Contact)

ダイナミック抵抗=TVS自身の抵抗成分が低いと、ESDを吸収しやすくなる。このダイナミック抵抗値が低いことで、図7で示す青丸枠の波形の傾きが緩やかになる。この傾きが緩くなると、破壊電圧に到達するまでの電流印可量(縦軸)が増える為、耐圧が上がる事になる。

ダイナミック抵抗の低いTVSでは、スナップバック特性には影響を与えることなくスナップバックした後の電圧上昇の傾きを緩くすることに寄与、すなわち、ICを保護する能力を向上させている。

図7 TLPグラフ他社製品比較

(縦軸:TLP電流(A)、横軸:TLP電圧(V))

(縦軸:TLP電流(A)、横軸:TLP電圧(V))

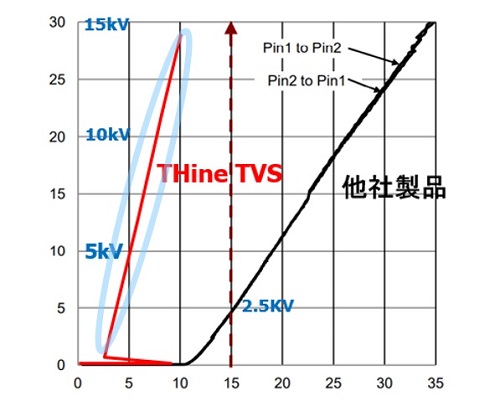

TVSラインナップ

当社のTVSは1チャンネル製品の他に、差動ラインへの配置にも適している2チャンネル、4チャンネル製品もラインナップしている。図8の3製品が第1期リリース製品だ。(→ラインナップはこちら)

図8 第1期リリース製品ラインアップ

最適な使用箇所

一番得意とするのは高速デジタル信号ラインの保護だ。上述したHDMI、DisplayPort、Thunderbolt、USB3.1、3.2、4.0など高速ラインでの差動伝送を保護、シングルエンド伝送、伝送路の堅牢性を担保する。デジタル信号例としては、CML, Ethernet, LVDS(EIA/TIA 644), MIPI DSI, MIPI CSI-2, FPD-LINK, eDP, SLVS-EC等がある。

また、近年のSoCやFPGA等のホストデバイスのESD耐性が全般的に低下していることを受け、ケーブル接続された基板上のコネクタ部で使用される各種汎用I/Oの保護も必要となってきており、基板上のコネクタ端に置かれることも増えている。特にType-Cコネクタでは多くのTVSが使われている。

伝送速度が高速化してきた時代にはそれに合ったTVSを選択することが必要となってくるだろう。

以上

また、近年のSoCやFPGA等のホストデバイスのESD耐性が全般的に低下していることを受け、ケーブル接続された基板上のコネクタ部で使用される各種汎用I/Oの保護も必要となってきており、基板上のコネクタ端に置かれることも増えている。特にType-Cコネクタでは多くのTVSが使われている。

伝送速度が高速化してきた時代にはそれに合ったTVSを選択することが必要となってくるだろう。

以上