THine Value 「V-by-OneⓇ」SerDes 기술은 액정TV의 어플리케이션뿐만 아니라, 통신/컴퓨터/산업 기계 등의 고속 인터페이스에서도 적용 가능한 기술

2019.11.08

- 기사

- 칼럼

자인 일렉트로닉스는, 1 Lane당 전송 속도가 최대 16Gbps인 고속 SerDes 및 시리얼 인터페이스 기술 「V-by-OneⓇ US」를 개발했다. 전세대의 「V-by-OneⓇ HS」와 비교하면 전송 속도는 4배가 된다. 8K 해상도의 액정TV 등에 액정 타이밍 컨트롤러 IC와 비디오 처리 보드를 접속하는 인터페이스에 사용한다. 어플리케이션은 단지 그뿐만이 아니다. 「V-by-OneⓇ US」에서 사용되는 물리층의 기술은 통신기기나 컴퓨터 기기 등에서 A지점과 B지점을 접속하는 고속 인터페이스에도 전용 가능한 기술이다. 이번에는, V-by-OneⓇ US의 특징과 구성을 해설하고, 고속 인터페이스를 사용하는 다른 어플리케이션에도 이 물리층 기술을 응용할 수 있는 이유를 해설한다.

브랜드 이미지의 빛과 그림자

자인 일렉트로닉스라고 하면 액정TV의 디지털 인터페이스 「V-by-OneⓇ HS」를 제공하는 반도체 업체라는 이미지가 매우 강하다. 기업 이미지가 확립되는 것은 결코 나쁜 것이 아니다. 액정TV를 개발하는 전자기기 제조업체는 액정 타이밍 컨트롤러 IC(T-CON)와 비디오 처리 보드를 접속하는 인터페이스를 검토할 때 반드시 「자인」이라는 기업명이나 「V-by-OneⓇ HS」라는 브랜드명이 머리를 스치기 때문이다.

그러나, 한편으로 단점이 있는 것도 사실이다. 그것은 「V-by-OneⓇ HS는 액정TV 전용」이라는 잘못된 이미지를 갖게 되는 것이다. 그 결과, 케이스간이나 기판간을 접속하는 고속 시리얼 전송이나 통신기기 등의 용도에서는 「자인」이라는 선택지가 누락될 위험성이 높다.

그러나, 한편으로 단점이 있는 것도 사실이다. 그것은 「V-by-OneⓇ HS는 액정TV 전용」이라는 잘못된 이미지를 갖게 되는 것이다. 그 결과, 케이스간이나 기판간을 접속하는 고속 시리얼 전송이나 통신기기 등의 용도에서는 「자인」이라는 선택지가 누락될 위험성이 높다.

최초의 타겟 시장은 액정TV였다

사실 V-by-OneⓇ HS는 액정TV의 인터페이스 이외의 다양한 용도로 사용되는 디바이스다(Fig.1). A지점에서 B지점으로 정보를 전달하는 고속의 범용 시리얼 인터페이스로서 다양한 어플리케이션에 채용되고 있다.

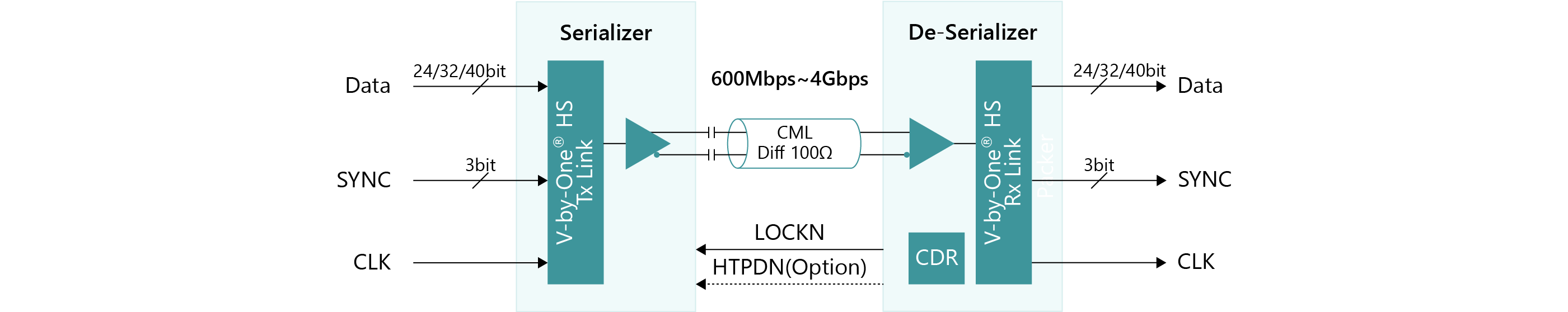

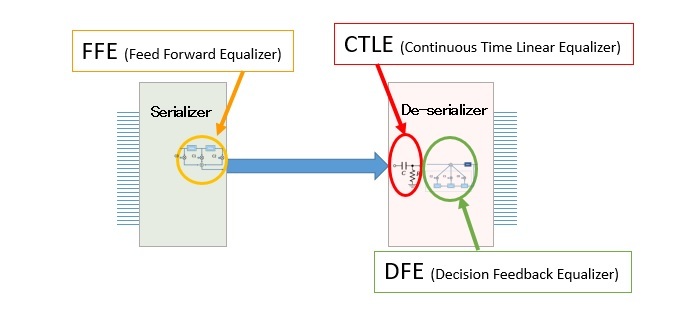

기술적으로 보면, V-by-OneⓇ HS는 단순한 「SerDes 칩」이다. SerDes란, Serializer와 Deserializer를 조합한 기술용어이다. Serializer에서 병렬 신호를 시리얼 신호로 변환하고, 1쌍의 신호 라인을 사용하여 고속으로 데이터를 송신한다(Fig.2). 그리고, 수신한 데이터를 Deserializer에서 시리얼 신호로부터 병렬 신호로 되돌린다.

자인 일렉트로닉스는, 시장이 급확대하던 고정밀 액정TV라는 시장에 재빨리 조준을 맞춰 「액정TV의 표준규격품」으로서 고속 시리얼 인터페이스인 V-by-OneⓇ HS 시리즈를 제품화했다. 다만, 그 기본적인 요소는 반도체 업체가 다양한 어플리케이션용으로 제품화하고 있는 SerDes 칩과 같은 것이다.

확실히, V-by-OneⓇ HS에서는 「R(Red)(0-9), G(Green)(0-9), B(Blue)(0-9)」나 「Vsync, Hsync, De」와 같은 액정TV 케이스 내의 T-CON과 비디오 처리 보드를 접속한 TTL/CMOS나 LVDS SerDes의 인터페이스 신호를 그대로 사용하고 있다. 그러나 그것은 어디까지나 액정TV라는 어플리케이션에서 적용하는 것을 상정해 붙인 명칭에 지나지 않는다. 다른 신호명을 사용하는 범용 고속 시리얼 인터페이스에서도 신호명에 얽매이지 않고 활용하는 것이 가능하다. (화이트 페이퍼: 일반적인 데이터 통신에서 V-by-One® HS 활용 참조)

Fig.1 V-by-OneⓇ HS 어플리케이션의 예

기술적으로 보면, V-by-OneⓇ HS는 단순한 「SerDes 칩」이다. SerDes란, Serializer와 Deserializer를 조합한 기술용어이다. Serializer에서 병렬 신호를 시리얼 신호로 변환하고, 1쌍의 신호 라인을 사용하여 고속으로 데이터를 송신한다(Fig.2). 그리고, 수신한 데이터를 Deserializer에서 시리얼 신호로부터 병렬 신호로 되돌린다.

Fig.2 Serializer와 De-serializer

자인 일렉트로닉스는, 시장이 급확대하던 고정밀 액정TV라는 시장에 재빨리 조준을 맞춰 「액정TV의 표준규격품」으로서 고속 시리얼 인터페이스인 V-by-OneⓇ HS 시리즈를 제품화했다. 다만, 그 기본적인 요소는 반도체 업체가 다양한 어플리케이션용으로 제품화하고 있는 SerDes 칩과 같은 것이다.

확실히, V-by-OneⓇ HS에서는 「R(Red)(0-9), G(Green)(0-9), B(Blue)(0-9)」나 「Vsync, Hsync, De」와 같은 액정TV 케이스 내의 T-CON과 비디오 처리 보드를 접속한 TTL/CMOS나 LVDS SerDes의 인터페이스 신호를 그대로 사용하고 있다. 그러나 그것은 어디까지나 액정TV라는 어플리케이션에서 적용하는 것을 상정해 붙인 명칭에 지나지 않는다. 다른 신호명을 사용하는 범용 고속 시리얼 인터페이스에서도 신호명에 얽매이지 않고 활용하는 것이 가능하다. (화이트 페이퍼: 일반적인 데이터 통신에서 V-by-One® HS 활용 참조)

고화질화가 전송 속도를 끌어올리다

게다가, 놓칠 수 없는 것은 액정TV의 디지털 인터페이스의 데이터 전송 속도의 높이다. 액정TV의 고화질화가 급속히 진행되고 있기 때문에, 그에 따른 인터페이스의 데이터 전송 속도 요구도 급속히 높아지고 있다. 구체적으로는 고해상도화와 High Frame Rate(HFR)화, High Dynamic Range(HDR)화인 3개의 움직임이 동시 진행 중이다.

그 결과, 인터페이스의 데이터 전송 속도는 매우 높은 수준에 도달해 있다. 예를 들면, 4K, 60Fps, 10Bit RGB 영상 신호의 경우, 스루풋은 V-by-OneⓇ HS에서는 24Gbps가 필요하다. V-by-OneⓇ HS에서는 3Gbps×8Lane으로 이 고속 인터페이스를 실현했다. 「그러나, 고객은 60Fps로는 만족하지 않는다. 예를 들면, 큰화면으로 축구 중계를 보면 60Fps에서는 공이 흐릿하게 보이지만, 120Fps에서는 선명하고 더욱 생동감을 더한다.」(자인). 4K, 120Fps, 10Bit 컬러가 되면, 스루풋은 2배인 48Gbps에 달한다.

게다가 해상도에 대해서는 세계적으로 8K로의 이행이 시작되고 있다. 이미 일본내애서는 NHK에서 8K에 대응한 실험 방송이 개시되었다. 8K가 되면, V-by-OneⓇ HS에서의 스루풋은 60Fps・10Bit・컬러에서 96Gbps에, 120Fps・10Bit・컬러에서 192Gbps에 도달한다.

그 결과, 인터페이스의 데이터 전송 속도는 매우 높은 수준에 도달해 있다. 예를 들면, 4K, 60Fps, 10Bit RGB 영상 신호의 경우, 스루풋은 V-by-OneⓇ HS에서는 24Gbps가 필요하다. V-by-OneⓇ HS에서는 3Gbps×8Lane으로 이 고속 인터페이스를 실현했다. 「그러나, 고객은 60Fps로는 만족하지 않는다. 예를 들면, 큰화면으로 축구 중계를 보면 60Fps에서는 공이 흐릿하게 보이지만, 120Fps에서는 선명하고 더욱 생동감을 더한다.」(자인). 4K, 120Fps, 10Bit 컬러가 되면, 스루풋은 2배인 48Gbps에 달한다.

게다가 해상도에 대해서는 세계적으로 8K로의 이행이 시작되고 있다. 이미 일본내애서는 NHK에서 8K에 대응한 실험 방송이 개시되었다. 8K가 되면, V-by-OneⓇ HS에서의 스루풋은 60Fps・10Bit・컬러에서 96Gbps에, 120Fps・10Bit・컬러에서 192Gbps에 도달한다.

16Gbps×16 Lane에 대응 완료

이미 자인 일렉트로닉스에서는, 8K, 120Fps의 영상 신호에 대응하는 솔루션을 확립하고 있다. 그것이 V-by-OneⓇ HS의 차세대판인 「V-by-OneⓇ US」다. 1Lane당 최대 데이터 전송 속도는 V-by-OneⓇ HS의 4배인 16Gbps에 달한다. 그것을 16Lane 묶음으로 8K, 120Fps의 영상 신호에 대응한다. 또한, 색심도가 12Bit・컬러면 1Lane당 14.85Gbps, 10Bit・컬러면 11.88Gbps가 된다.

즉, 이러한 사실은 이미 자인 일렉트로닉스에서는 16Gbps×16Lane의 범용 인터페이스 기술을 확립하고 있음을 의미한다. 이 고속 전송의 물리층 기술은 액정TV의 디지털 인터페이스 뿐만 아니라, 긴 케이블을 통한 영상 전송이나 A지점과 B지점을 고속으로 연결하는 데이터 전송의 인터페이스에서도 그대로 전용할 수 있는 기술이다.

즉, 이러한 사실은 이미 자인 일렉트로닉스에서는 16Gbps×16Lane의 범용 인터페이스 기술을 확립하고 있음을 의미한다. 이 고속 전송의 물리층 기술은 액정TV의 디지털 인터페이스 뿐만 아니라, 긴 케이블을 통한 영상 전송이나 A지점과 B지점을 고속으로 연결하는 데이터 전송의 인터페이스에서도 그대로 전용할 수 있는 기술이다.

FFE, CTLE, DFE를 활용

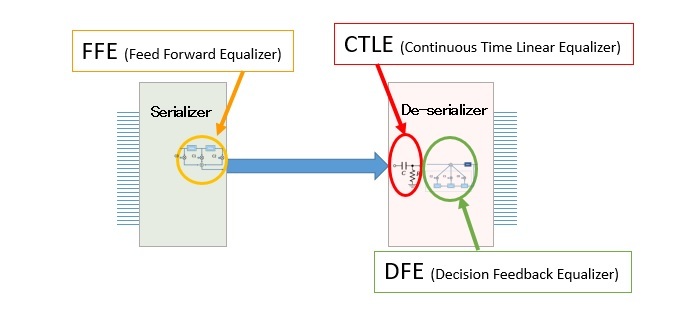

그러면, V-by-OneⓇ US는 어떤 물리층의 기술을 사용하여 이 고속화를 실현하고 있는 것일까? 기본적으로 10~28Gbps 대역의 데이터 통신 어플리케이션의 SerDes나 리타이머(CDR)에서 일반적으로 사용되고 있는 복수의 시그널 컨디셔닝을 이용하여 실현하고 있다. 송신 회로(Transmitter)에 FFE(Feed-Forward Equalizer)를, 수신 회로(Receiver)에 DFE(Decision Feedback Equalizer)와 CTLE(Continuous Time Linear Equalizer)를 적용하고 있다(Fig.3).

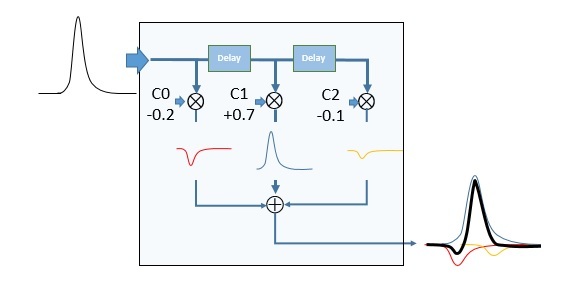

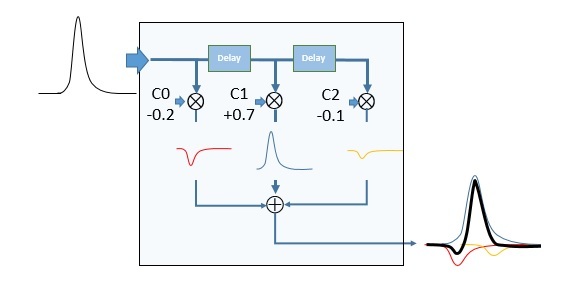

여기서, 각각의 기술을 간단히 설명하자. 트랜스미터에 사용되고 있는 FFE는 디엠퍼시스나 프리엠퍼시스의 기능을 포함하고 있어 실제로는 그보다 섬세한 파형 조정이 가능한 기술이다. 전송로에서 감쇠해 버리는 고주파 성분을 미리 송신단에서 증폭시켜 둔다. 구체적으로는 복수의 지연(Delay 블럭)으로 각 탭을 준비하고, 1UI(Unit Interval)마다 각 탭의 임의의 계수(비율)에서 증폭이나 감쇠시킨 신호를 ⊕부에서 서로 더하고, 출력하고 있다(Fig.4).

이렇게 함으로써 파형의 (프리・디)엠퍼시스 뿐만이 아니라, 프리슈트를 포함한 임의의 송신 파형을 만들 수 있어 수신단에서 EYE의 시간축 방향의 개구가 커지도록 설정한다.

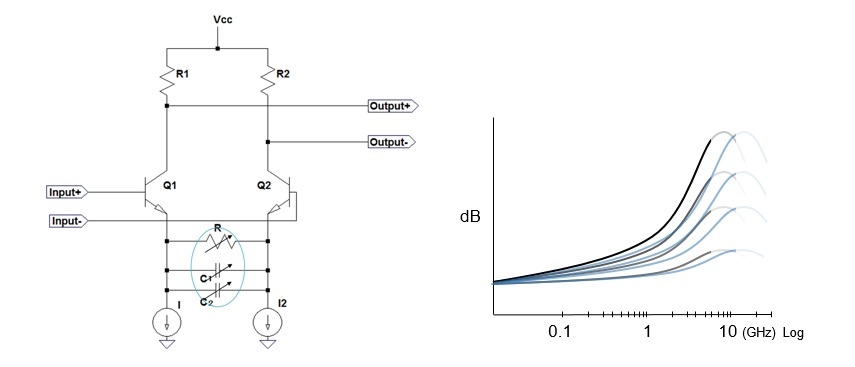

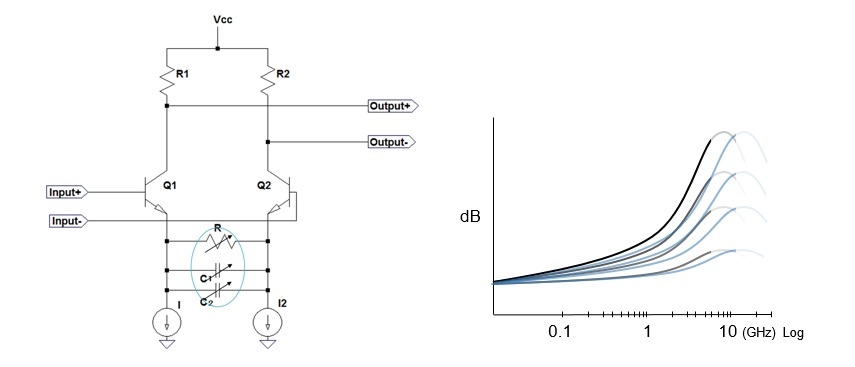

수신측의 CTLE는, 일본어에서는 연속 시간 Linear Equalizer라고 부르며, 전송로에서 잃어버린 고주파 성분을 증폭하고 보상하는 기술이다(Fig.5). 즉, 전송로의 저주파 통과 필터 특성을 보상하는 고주파 통과 필터와 증폭기로 기능한다.

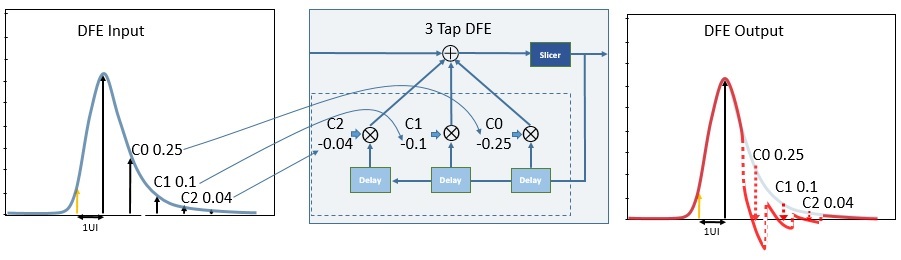

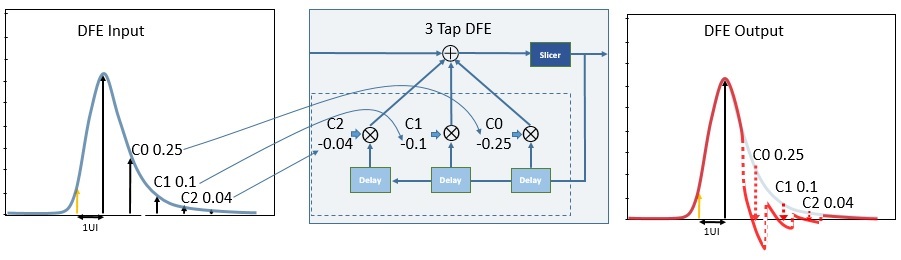

Receiver측에 적용하는 또 하나의 기술인 DFE는, 수신단 파형의 심볼간 간섭(ISI:Inter Symbol Interference)의 Jitter를 지우는 기술이다. FFE와 마찬가지로, 수신 신호에 복수의 Delay를 건 각 신호(Tap)를 준비한다(Fig.6). 그리고 수신한 파형과 이상적인 파형과의 오차가 최소가 되도록 1UI마다 각 탭의 계수를 구하고, 이것을 수신 신호에 대해서 피드백을 준다. 이렇게 함으로써 Jitter를 저감하여 Eye 개구가 큰 신호 파형으로 되돌리는 것이다.

또한, CTLE와 DFE의 역할 분담으로서는 완전히 Eye가 닫혀버린 수신 파형에 대하여, 우선은 CTLE를 적용해서 Eye를 어느정도 여는 처리를 한다. 그 후, DFE에서 Jitter를 더욱 저감하여 Eye 개구를 더 크게 하고 있다.

Fig.3 전송 회로에 FFE, 송신 회로에 CTLE와 DFE의 시그널 컨디셔닝을 적용

여기서, 각각의 기술을 간단히 설명하자. 트랜스미터에 사용되고 있는 FFE는 디엠퍼시스나 프리엠퍼시스의 기능을 포함하고 있어 실제로는 그보다 섬세한 파형 조정이 가능한 기술이다. 전송로에서 감쇠해 버리는 고주파 성분을 미리 송신단에서 증폭시켜 둔다. 구체적으로는 복수의 지연(Delay 블럭)으로 각 탭을 준비하고, 1UI(Unit Interval)마다 각 탭의 임의의 계수(비율)에서 증폭이나 감쇠시킨 신호를 ⊕부에서 서로 더하고, 출력하고 있다(Fig.4).

Fig.4 FFE(Feed Forward Equalizer)의 구조

이렇게 함으로써 파형의 (프리・디)엠퍼시스 뿐만이 아니라, 프리슈트를 포함한 임의의 송신 파형을 만들 수 있어 수신단에서 EYE의 시간축 방향의 개구가 커지도록 설정한다.

수신측의 CTLE는, 일본어에서는 연속 시간 Linear Equalizer라고 부르며, 전송로에서 잃어버린 고주파 성분을 증폭하고 보상하는 기술이다(Fig.5). 즉, 전송로의 저주파 통과 필터 특성을 보상하는 고주파 통과 필터와 증폭기로 기능한다.

Fig.5 CTLE(Continuous Time Linear Equalizer)의 구조

Receiver측에 적용하는 또 하나의 기술인 DFE는, 수신단 파형의 심볼간 간섭(ISI:Inter Symbol Interference)의 Jitter를 지우는 기술이다. FFE와 마찬가지로, 수신 신호에 복수의 Delay를 건 각 신호(Tap)를 준비한다(Fig.6). 그리고 수신한 파형과 이상적인 파형과의 오차가 최소가 되도록 1UI마다 각 탭의 계수를 구하고, 이것을 수신 신호에 대해서 피드백을 준다. 이렇게 함으로써 Jitter를 저감하여 Eye 개구가 큰 신호 파형으로 되돌리는 것이다.

Fig.6 DFE(Decision Feedback Equalizer)의 구조

또한, CTLE와 DFE의 역할 분담으로서는 완전히 Eye가 닫혀버린 수신 파형에 대하여, 우선은 CTLE를 적용해서 Eye를 어느정도 여는 처리를 한다. 그 후, DFE에서 Jitter를 더욱 저감하여 Eye 개구를 더 크게 하고 있다.

FFC/커넥터 업체 각사와 V-by-OneⓇ US 전송로를 공동 개발

나아가 자인 일렉트로닉스는, V-by-OneⓇ US의 칩 개발에만 머무르지 않고, 고속 디지털 인터페이스의 전송로(Signal Path)인 플렉시블 플랫 케이블(FFC)과 커넥터 개발에도 FFC/커넥터 업체와 협력하여 전념하고 있다. FFC 업체, 커넥터 업체와 공동으로 광대역화의 기술 개발에 몰두하여, 이미 16Gbps×16Lane의 데이터를 1m 이상 전송할 수 있는 전송로 기술을 확립하고 있다.

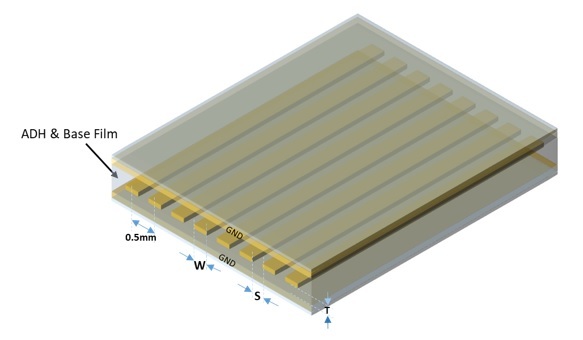

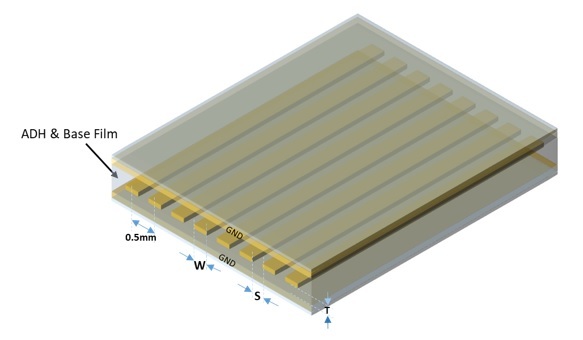

이 광대역 FFC에서는, 재료와 구조를 최적화하고 있다. 재료에는 유전정접(tanδ)과 비유전율(εr)이 모두 작은 것을 채용하여 기본적인 손실 특성을 향상시키고, 또 전송로의 W(폭)・S(공간)・T(두께)의 레이아웃(Fig.7)을 고려하고, 전송손실, 반사손실, 크로스토크를 최소화했다.

리셉터클 커넥터에 대해서도, 현행품의 형상을 답습하면서도 기판과의 납땜 접속부의 개선이나 금속 부분의 개선, 커넥터내 배선 길이의 조정 등으로 임피던스 정합을 확보하고, 고속 전송 시의 신호 반사를 저감하고 있다.

다만, 16Gbps×16Lane의 범용 인터페이스를 구축할 때의 과제는 아직 남아 있다고 한다. 그것은, V-by-OneⓇ US 대응 칩이나 커넥터를 실장하는 프린트 기판의 설계이다. 이 프린트 기판의 설계에 자인 일렉트로닉스가 개입하기는 어렵다. 어디까지나 고객측의 작업이기 때문이다. 자인 일렉트로닉스에 따르면, 「프린트 기판의 재질과 층구조가 전기적인 특성에 큰 영향을 주기 때문에 고속 신호의 아트워크에 주의가 필요하며, 또 각 부품과의 접속점의 임피던스 컨트롤이 중요하다」고 한다.

이 광대역 FFC에서는, 재료와 구조를 최적화하고 있다. 재료에는 유전정접(tanδ)과 비유전율(εr)이 모두 작은 것을 채용하여 기본적인 손실 특성을 향상시키고, 또 전송로의 W(폭)・S(공간)・T(두께)의 레이아웃(Fig.7)을 고려하고, 전송손실, 반사손실, 크로스토크를 최소화했다.

Fig.7 16Gbps에 대응한 FFC의 기본 구조(양면 쉴드 타입)

리셉터클 커넥터에 대해서도, 현행품의 형상을 답습하면서도 기판과의 납땜 접속부의 개선이나 금속 부분의 개선, 커넥터내 배선 길이의 조정 등으로 임피던스 정합을 확보하고, 고속 전송 시의 신호 반사를 저감하고 있다.

다만, 16Gbps×16Lane의 범용 인터페이스를 구축할 때의 과제는 아직 남아 있다고 한다. 그것은, V-by-OneⓇ US 대응 칩이나 커넥터를 실장하는 프린트 기판의 설계이다. 이 프린트 기판의 설계에 자인 일렉트로닉스가 개입하기는 어렵다. 어디까지나 고객측의 작업이기 때문이다. 자인 일렉트로닉스에 따르면, 「프린트 기판의 재질과 층구조가 전기적인 특성에 큰 영향을 주기 때문에 고속 신호의 아트워크에 주의가 필요하며, 또 각 부품과의 접속점의 임피던스 컨트롤이 중요하다」고 한다.

차세대 디바이스 개발에 착수

현재, 자인 일렉트로닉스에서는 V-by-OneⓇ US를 크게 웃도는 전송 속도를 갖춘 차세대 디바이스의 요소 기술 개발에 몰두하고 있다. 고속 인터페이스용 디바이스의 라인업을 확충함으로써, 「고속 인터페이스의 자인」이라는 기업 이미지를 굳혀 나갈 생각이다.

전송 속도가 빠른 디바이스를 제품화하는 임팩트는 매우 크다. 이유는 2가지다. 하나는, 기술력의 높이를 어필할 수 있는 것이다. 기업 이미지에 높은 기술력이 더해지면, 고속 인터페이스 시장에서의 인지도를 순조롭게 높일 수 있을 것이다.

다른 이유는, 잠재 시장의 규모가 큰 것이다. 현재, 통신 인프라 시장이나 데이터 센터 시장에서도 더 높은 전송 속도를 가진 인터페이스 기술의 요구가 높아지고 있다. 통신 인프라 시장에서는, 5G(제5세대)에 대응이 요구되고 있기 때문에, 영상 신호 등을 지연 없이 전송하는 것이 요구되고 있다. 데이터 센터 시장에서는 AI(인공지능) 프로세서나 GPU 등의 연산 처리 능력이 매우 높아지고 있기 때문에, 칩간 데이터 전송에 더 넓은 대역을 필요로 하고 있다.

1Lane당 16Gbps를 크게 웃도는 디바이스의 실용화는 「액정TV의 자인」에서 「고속 인터페이스의 자인」으로 기업 이미지가 전환되는 타이밍이 될 수도 있다.

전송 속도가 빠른 디바이스를 제품화하는 임팩트는 매우 크다. 이유는 2가지다. 하나는, 기술력의 높이를 어필할 수 있는 것이다. 기업 이미지에 높은 기술력이 더해지면, 고속 인터페이스 시장에서의 인지도를 순조롭게 높일 수 있을 것이다.

다른 이유는, 잠재 시장의 규모가 큰 것이다. 현재, 통신 인프라 시장이나 데이터 센터 시장에서도 더 높은 전송 속도를 가진 인터페이스 기술의 요구가 높아지고 있다. 통신 인프라 시장에서는, 5G(제5세대)에 대응이 요구되고 있기 때문에, 영상 신호 등을 지연 없이 전송하는 것이 요구되고 있다. 데이터 센터 시장에서는 AI(인공지능) 프로세서나 GPU 등의 연산 처리 능력이 매우 높아지고 있기 때문에, 칩간 데이터 전송에 더 넓은 대역을 필요로 하고 있다.

1Lane당 16Gbps를 크게 웃도는 디바이스의 실용화는 「액정TV의 자인」에서 「고속 인터페이스의 자인」으로 기업 이미지가 전환되는 타이밍이 될 수도 있다.