## THTVS514

Transient Voltage Suppressor for I/O Protection

#### General Description

THTVS514 4ch TVS arrays are ultra-low capacitance ESD protection devices designed to protect sensitive or high speed I/O. Thine THTVS series has been specifically designed to protect sensitive components which are connected to digital transmission lines from overvoltage caused by ESD (electrostatic discharge), CDE (Cable Discharge Events), and EFT (electrical fast transients).

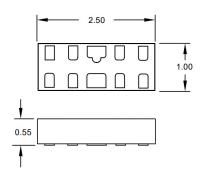

THTVS514 has a 0.3pF(typ) small capacitance between I/O pins. ESD are highlighted by high ESD withstand voltage (Contact  $\pm 12$ kV per IEC 61000-4-2), It will protect four lines operating at 5.5V(Vrwm). THTVS514 is in a 2.5 x 1.0 x 0.55mm 10-Lead standard package and flow-through pin layout for easy and simple PCB design.

The THTVS514 four-channel TVS is for sensitive or high speed I/O which designed to protect ASIC, FPGA, SoC, ASSP, LVDS, PECL, CML digital I/O and HDMI, Display port, USB3.0 high speed standard I/O.

They may be used to meet the ESD immunity requirements of IEC 61000-4-2/4/5.

The THTVS514 protects four single-end lines or two differential lines.

#### **Features**

- ESD protection for high-speed data lines to IEC61000-4-2(ESD) ±17kV (air), ±12kV (contact) IEC61000-4-4(EFT) 40A (5/50ns) IEC61000-4-5(Surge) 6A (8/20μs)

- Protect four high speed lines

- Flow-through pin configuration

- Low capacitance: 0.3pF typ (I/O to I/O)

- Low dynamic resistance: 0.19 Ohm typ

- Operating voltage: Vrwm 5.5V

- 10 pin standard package (2.5 x 1.0 x 0.55mm)

- Packaging: Tape and Reel

#### **Applications**

Applications for sensitive and high speed I/O protection as followed.

- FPGA/SoC/ASSP high speed I/O.

- CML/PECL/LVDS physical layer

- HDMI/DVI/DisplayPort<sup>TM</sup>

- PCI Express /eSATA

- USB3.0/3.1

- V-by-One<sup>®</sup> HS

- Sensitive Sensor I/O

- Connector and cable I/F

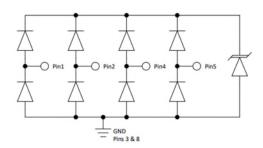

### **Schematic and Package Dimension**

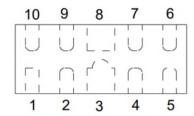

# Pin Configuration

THTVS514 package pin configuration (Top view)

## Pin Description

| Pin No         | Type  | Description                                  |

|----------------|-------|----------------------------------------------|

| 1              |       | Input                                        |

| 2              | I     | Input                                        |

| 3, 8           | GND*1 | Ground. Must be tied to the PCB ground plane |

| 4              | I     | Input                                        |

| 5              | I     | Input                                        |

| 6 ,7,<br>9 ,10 | NC    | No internal connection                       |

<sup>\*1:</sup> Low impedance connection to Ground required.

### **Absolute Maximum Rating**

| Parameter                                                          | Symbol           | Value            | Unit |

|--------------------------------------------------------------------|------------------|------------------|------|

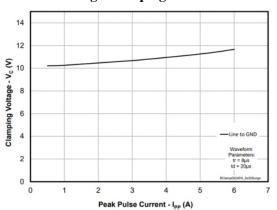

| Peak Pulse Current (tp = 8/20μs)                                   | I <sub>PP</sub>  | 6                | А    |

| ESD per IEC 61000-4-2 (Air) (1) ESD per IEC 61000-4-2 (Contact)(1) | V <sub>ESD</sub> | +/- 17<br>+/- 12 | kV   |

| Operating Junction Temperature                                     | T <sub>J</sub>   | -55 to +125      | °C   |

| Storage Temperature                                                | T <sub>STG</sub> | -55 to +150      | °C   |

Notes:

Copyright(C)2023 THine Electronics,Inc.

<sup>(1)</sup> ESD gun return path connected to Ground Reference Plane (GRP)

# Electrical Characteristics (Tj = 25 °C)

| Parameter                           | Symbol                        | Condition                                               | Min | Тур  | Max | Unit |

|-------------------------------------|-------------------------------|---------------------------------------------------------|-----|------|-----|------|

| Reverse Stand-Off<br>Voltage        | $V_{\scriptscriptstyle{RWM}}$ | I/O pin to ground                                       | -   | -    | 5.5 | V    |

| Reverse Breakdown<br>Voltage        | $V_{_{BR}}$                   | I <sub>t</sub> = 1mA<br>I/O pin to ground               | 6   | 1    | 1   | V    |

| Clamping Voltage                    | V <sub>c</sub>                | Ipp = 1A<br>tp = 8/20µs<br>Any I/O pin to GND           | -   | -    | 15  | V    |

| Reverse Leakage Current             | I <sub>R</sub>                | V <sub>RWM</sub> = 5.5V                                 | -   | -    | 0.1 | μΑ   |

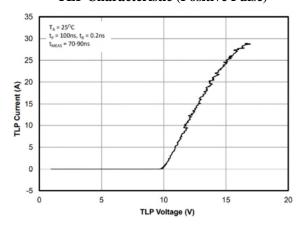

|                                     | V <sub>c</sub>                | Ipp = 4A<br>tp = 0.2/100ns (TLP)<br>Any I/O pin to GND  | -   | 10.8 | -   | V    |

| ESD Clamping Voltage <sup>(2)</sup> |                               | Ipp = 16A<br>tp = 0.2/100ns (TLP) Any<br>I/O pin to GND | -   | 13.0 | 1   |      |

| Dynamic Resistance (2)(3)           | $R_{\scriptscriptstyle DYN}$  | tp = 0.2/100ns (TLP)                                    | -   | 0.19 | -   | Ω    |

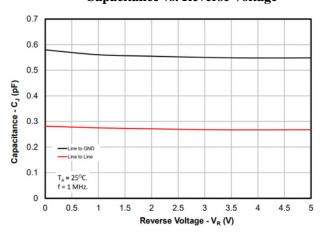

| Junatian Canasitanas                | C <sub>j</sub>                | $V_R = 0V$ , $f = 1MHz$<br>I/O Pins to ground           | 1   | 1    | 0.8 | _    |

| Junction Capacitance                |                               | $V_R = 0V$ , $f = 1MHz$<br>between I/O pins             | -   | 0.3  | 0.4 | pF   |

Notes:

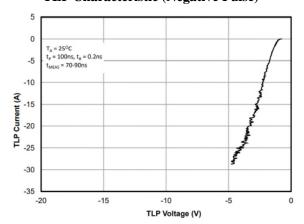

<sup>(2)</sup> Transmission Line Pulse Test (TLP) Settings: tp = 100ns, tr = 0.2ns, I\_TLP and V\_TLP averaging window: t1 = 70ns to t2 =

<sup>(3)</sup> Dynamic resistance calculated from  $I_TLP = 4A$  to  $I_TLP = 16A$

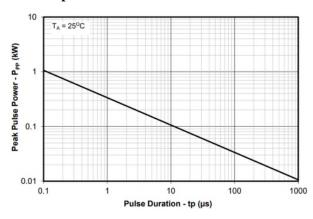

### **Typical Characteristics**

#### Non-Repetitive Peak Pulse Power vs. Pulse Time

#### 8/20us Surge Clamping Characteristic

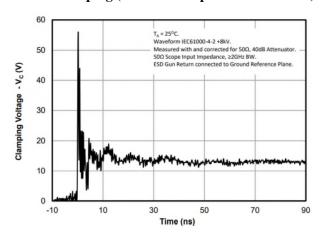

ESD Clamping (8kV Contact per IEC 61000-4-2)

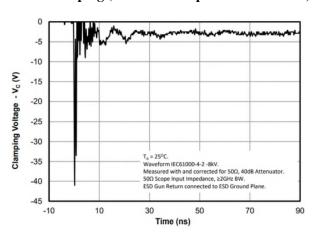

ESD Clamping (-8kV Contact per IEC 61000-4-2)

**TLP Characteristic (Positive Pulse)**

**TLP Characteristic (Negative Pulse)**

Copyright(C)2023 THine Electronics, Inc.

## **Typical Characteristics**

#### Capacitance vs. Reverse Voltage

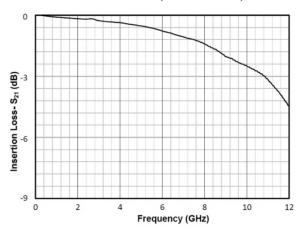

#### **Insertion Loss (Line to GND)**

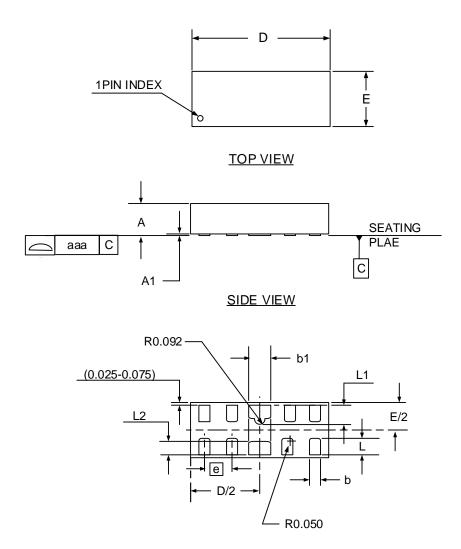

## **Package**

**BOTTOM VIEW**

Unit: mm

| Symbol | Items           | Min.     | Nom.  | Max.  |  |

|--------|-----------------|----------|-------|-------|--|

| Α      | Mounting Height | 0.50     | 0.55  | 0.60  |  |

| A1     | Standoff        | 0.00     | 0.03  | 0.05  |  |

| b      | -               | 0.15     | 0.20  | 0.25  |  |

| b1     | -               | 0.35     | 0.40  | 0.45  |  |

| D      | Body Length     | 2.45     | 2.50  | 2.575 |  |

| E      | Body Width      | 0.95     | 1.00  | 1.075 |  |

| е      | Pitch           | 0.50 BSC |       |       |  |

| L      | -               | 0.25     | 0.30  | 0.35  |  |

| L1     | -               | 0.30     | 0.35  | 0.40  |  |

| L2     | -               | 0.194    | 0.244 | 0.294 |  |

| aaa    | Coplanarity     | 0.08     |       |       |  |

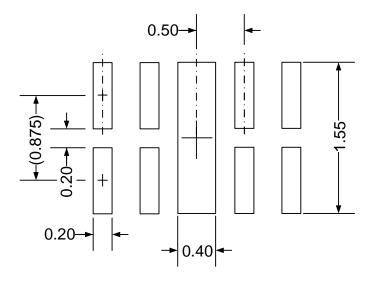

# **Land Pattern**

#### Note:

Please carefully consider your SMT conditions (Material of substrate, Solder Composition, Reflow Condition and so on), and adjusts the Land Pattern at your own risk.

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other intellectual property rights. Copying, reverse-engineer or disclosing to third parties the contents of this material without THine's prior written permission is prohibited.

- 4. THINE ACCEPTS NO LIABILITY FOR ANY DAMAGE OR LOSS IN CONNECTION WITH ANY DISPUTE RELATING TO INTELLECTUAL PROPERTY RIGHTS BETWEEN THE USER AND ANY THIRD PARTY, ARISING OUT OF THIS PRODUCT, EXCEPT FOR SUCH DAMAGE OR LOSS IN CONNECTION WITH DISPUTES SUCCESSFULLY PROVED BY THE USER THAT SUCH DISPUTES ARE DUE SOLELY TO THINE. NOTE, HOWEVER, EVEN IN THE AFOREMENTIONED CASE, THINE ACCEPTS NO LIABILITY FOR SUCH DAMAGE OR LOSS IF THE DISPUTE IS CAUSED BY THE USER'S INSTRUCTION.

- 5. This product is not designed for applications that require extremely high-reliability/safety such as aerospace device, nuclear power control device, or medical device related to critical care, excluding when this product is specified for automotive use by THine and used it for that purpose. THine accepts no liability whatsoever for any damages, claims or losses arising out of the uses set forth above.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently fail-safe design principles such as redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. This product may be permanently damaged and suffer from performance degradation or loss of mechanical functionality if subjected to electrostatic charge exceeding capacity of the ESD (Electrostatic Discharge) protection circuitry. Safety earth ground must be provided to anything in contact with the product, including any operator, floor, tester and soldering iron

- 8. Please note that this product is not designed to be radiation-proof.

- 9. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 10. This product must be stored according to storage method which is specified in this specifications. THine accepts no liability whatsoever for any damage or loss caused to the user due to any storage not according to above-mentioned method.

- 11. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act in Japan and the Export Administration Regulations in the United States of America on export or transit of this product. This product is prohibited for the purpose of developing military modernization, including the development of weapons of mass destruction (WMD), and the purpose of violating human rights.

Copyright(C)2023 THine Electronics, Inc.

- 12. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition.

Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses. Thine accepts no liability whatsoever for any damage or loss caused to the user due to use under a condition exceeding the limiting values.

- 13. All patents or pending patent applications, trademarks, copyrights, layout-design exploitation rights or other intellectual property rights concerned with this product belong to THine or licensor(s) of THine. No license or right is granted to the user for any intellectual property right or other proprietary right now or in the future owned by THine or THine's licensor. The user must enter into a license agreement with THine or THine's licensor to be granted of such license or right.

## THine Electronics, Inc.

https://www.thine.co.jp

Copyright(C)2023 THine Electronics, Inc.