# THC63LVD1027

#### Dual Link LVDS Repeater

#### General Description

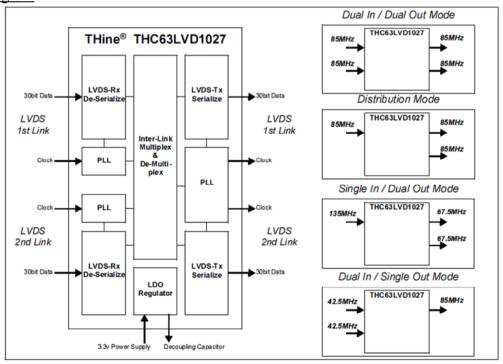

The THC63LVD1027 LVDS(Low Voltage Differential Signaling) repeater is designed to support pixel data transmission between Host and Flat Panel Display up to WUXGA resolution.

THC63LVD1027 receives the dual link LVDS data streams and transmits the LVDS data through various line rate conversion modes, Dual Link Input / Dual Link Output, Single Link Input / Dual Link Output, and Dual Link Input / Single Link Output.

#### Features

- 30bits/pixel dual link LVDS Receiver

- 30bits/pixel dual Link LVDS Transmitter

- Operating Temperature Range : -40°C~85°C

- Wide LVDS input skew margin: ± 480ps at 75MHz

- Accurate LVDS output timing: ± 250ps at 75MHz

- Reduced swing LVDS output mode supported to suppress the system EMI

- Various line rate conversion modes supported Dual link input / Dual link output [clkout=1x clkin] Single link input / Dual link output [clkout=1/2x clkin] Dual link input / Single link output [clkout=2x clkin]

- Distribution (signal duplication) mode supported

- Power down mode supported

- 3.3V single voltage power supply

- No external components required for PLLs

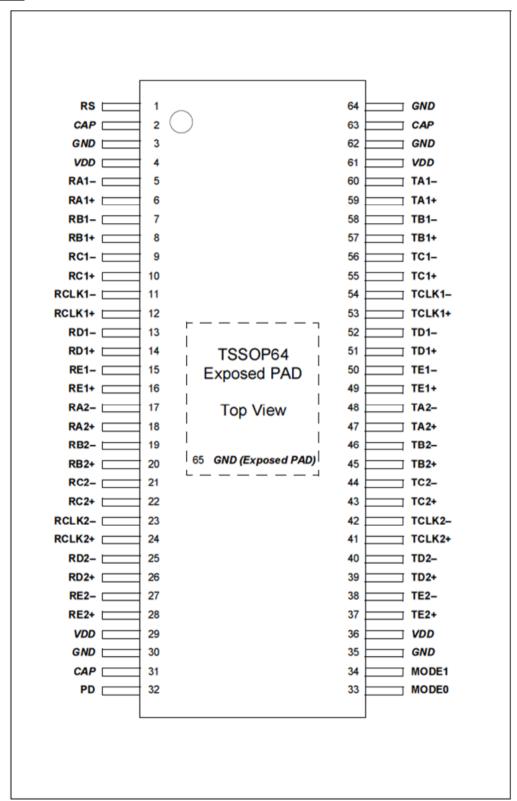

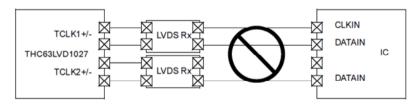

- 64pin TSSOP with Exposed PAD (0.5mm lead pitch)

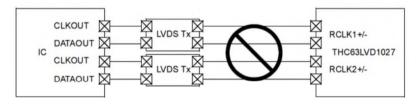

#### **Block Diagram**

Figure 1. Block Diagram

#### Pin Diagram

Figure 2. Pin Diagram

# Pin Description

Table 1. Pin Description

| Pin Name Direction Type Description  RA1+/-  RB1+/-  RC1+/-  RD1+/-  RD1+/-  RC1+/-  RCLK1+/-  RA2+/-  Input  Description  LVDS data input for channel A of 1st Link  LVDS data input for channel C of 1st Link  LVDS data input for channel D of 1st Link  LVDS data input for channel E of 1st Link  LVDS data input for channel E of 1st Link  LVDS clock input for 1st Link  LVDS data input for channel A of 2nd Link |                                                                                                   |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| RB1+/- RC1+/- RD1+/- RE1+/- RCLK1+/- RCLK1+/- RA2+/- Input  LVDS data input for channel B of 1st Link LVDS data input for channel C of 1st Link LVDS data input for channel D of 1st Link LVDS data input for channel E of 1st Link LVDS clock input for 1st Link LVDS data input for channel A of 2nd Link                                                                                                                |                                                                                                   |  |  |  |  |  |  |

| RC1+/- RD1+/- RE1+/- RCLK1+/- RCLK1+/- RA2+/- Input  LVDS data input for channel C of 1st Link LVDS data input for channel D of 1st Link LVDS data input for channel E of 1st Link LVDS clock input for 1st Link LVDS data input for channel A of 2nd Link                                                                                                                                                                 |                                                                                                   |  |  |  |  |  |  |

| RD1+/- RE1+/- RCLK1+/- RA2+/- Input  LVDS data input for channel D of 1st Link LVDS data input for channel E of 1st Link LVDS clock input for 1st Link LVDS data input for channel A of 2nd Link                                                                                                                                                                                                                           |                                                                                                   |  |  |  |  |  |  |

| RE1+/- RCLK1+/- RA2+/- Input  LVDS data input for channel E of 1st Link LVDS clock input for 1st Link LVDS data input for channel A of 2nd Link                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |  |  |  |

| RCLK1+/- RA2+/- Input  LVDS clock input for 1st Link LVDS data input for channel A of 2nd Link                                                                                                                                                                                                                                                                                                                             |                                                                                                   |  |  |  |  |  |  |

| RA2+/- Input LVDS data input for channel A of 2nd Link                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                   |  |  |  |  |  |  |

| Input I                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                   |  |  |  |  |  |  |

| RB2+/- LVDS data input for channel B of 2nd Link                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   |  |  |  |  |  |  |

| RC2+/-  LVDS data input for channel C of 2nd Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| RD2+/-  LVDS data input for channel D of 2nd Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | LVDS data input for channel E of 2nd Link  LVDS data input for channel E of 2nd Link              |  |  |  |  |  |  |

| RCLK2+/-  RCLK2+/-  LVDS clock input for 2nd Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| INDS In Distribution and Single-in/Dual-out mode,RCLK2+/- must                                                                                                                                                                                                                                                                                                                                                             | t be Hi-Z.                                                                                        |  |  |  |  |  |  |

| (See Mode selection below in this page.)                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |  |  |  |  |  |  |

| TA1+/- LVDS data output for channel A of 1st Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| TB1+/- LVDS data output for channel B of 1st Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| TC1+/- LVDS data output for channel C of 1st Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| TD1+/- LVDS data output for channel D of 1st Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| TE1+/- LVDS data output for channel E of 1st Link                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                   |  |  |  |  |  |  |

| TCLK1+/- Output  Output  LVDS clock output for 1st Link                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                   |  |  |  |  |  |  |

| LVDS data output for channel A of 2nd Lini                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                          | LVDS data output for channel B of 2nd Link                                                        |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | LVDS data output for channel C of 2nd Link                                                        |  |  |  |  |  |  |

| TD2+/- LVDS data output for channel D of 2nd Lin                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   |  |  |  |  |  |  |

| TE2+/- LVDS data output for channel E of 2nd Link                                                                                                                                                                                                                                                                                                                                                                          | k                                                                                                 |  |  |  |  |  |  |

| TCLK2+/- LVDS clock output for 2nd Link                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                   |  |  |  |  |  |  |

| PD Power Down                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                   |  |  |  |  |  |  |

| H: Normal operation L: Power down state, all LVDS output signals turn to Hi-Z                                                                                                                                                                                                                                                                                                                                              |                                                                                                   |  |  |  |  |  |  |

| RS LVDS output swing level selection                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                   |  |  |  |  |  |  |

| H: Normal swing                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |  |  |  |

| L: Reduced swing                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   |  |  |  |  |  |  |

| MODE1 Input LV-TTL Mode selection MODE1 MODE0 RCLK2+/- Descript                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |  |  |  |

| MODE0 MODE0 MODE0 RCLK2+/- Descript L L Clkin Dual-in/Dual-                                                                                                                                                                                                                                                                                                                                                                |                                                                                                   |  |  |  |  |  |  |

| L L Hi-Z Distribution                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |  |  |  |  |  |  |

| H L Hi-Z Single-in/Dual                                                                                                                                                                                                                                                                                                                                                                                                    | -out mode                                                                                         |  |  |  |  |  |  |

| L H Clkin Dual-in/Single                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | H H - Reserved  In Distribution and Single-in/Dual-out mode, RCLK2+/- must be Hi-Z.               |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | st be H1-Z.                                                                                       |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.3V power supply pins  Crownd ping (Ermand PAD is also Crownd)                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | Ground pins (Exposed PAD is also Ground)                                                          |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                            | Decoupling capacitor pins These pins should be connected to external decoupling capacitors(Ccap). |  |  |  |  |  |  |

| Recommended Ccap is 0.1µF.                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |  |  |  |

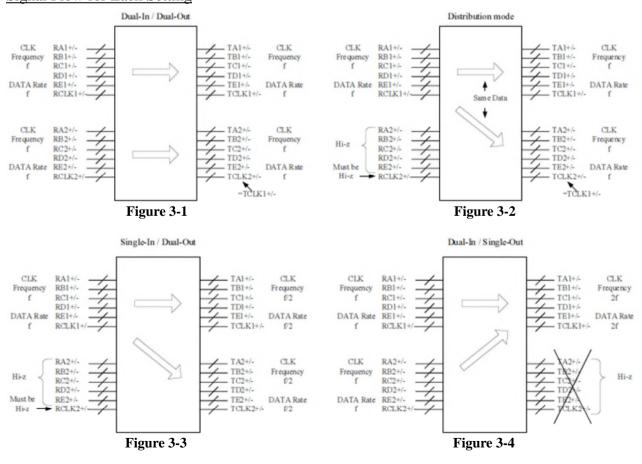

#### Mode Setting

**Table 2. Mode Setting**

| Input/Output       | RCLK2+/- | MODE1        | MODE0         |

|--------------------|----------|--------------|---------------|

|                    |          | (Input mode) | (Output mode) |

|                    |          | H: Single    | H: Single     |

|                    |          | L: Dual      | L: Dual       |

| Dual-In/Dual-Out   | CLK in   | L            | L             |

| (Fig.3-1,14-1)     |          |              |               |

| Distribution       | Hi-Z     | L            | L             |

| (Fig.3-2,14-2)     |          |              |               |

| Single-In/Dual-Out | Hi-Z     | Н            | L             |

| (Fig.3-3,14-3)     |          |              |               |

| Dual-In/Single-Out | CLK in   | L            | Н             |

| (Fig.3-4,14-4)     |          |              |               |

| Reserved           | -        | Н            | Н             |

#### Signal Flow for Each Setting

## Output Control / Fail Safe

THC63LVD1027 has a function to control output depending on LVDS input condition.

**Table 3. Output Control**

| PD | RCLK1+/- | RCLK2+/- | Output                      |

|----|----------|----------|-----------------------------|

| L  | *        | *        | All Hi-Z                    |

| Н  | Hi-Z     | *        | All Hi-Z                    |

| Н  | CLK in   | CLK in   | Refer to p.4 Mode Setting # |

| Н  | CLK in   | Hi-Z     | Refer to p.4 Mode Setting # |

<sup>\*:</sup> Don't care

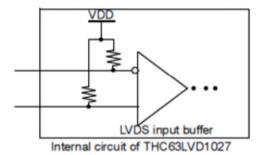

For fail-safe purpose, all LVDS input pins are connected to VDD via resistance for detecting Hi-Z state.

Figure 4. Fail Safe Circuit

<sup>#:</sup> If a particular input data pair is Hi-Z, the corresponding output data become L according to LVDS DC spec.

# Absolute Maximum Ratings

**Table 4. Absolute Maximum Rating**

| Parameter                        | Min  | Max                  | Unit |

|----------------------------------|------|----------------------|------|

| Power Supply Voltage             | -0.3 | +4.0                 | V    |

| LVCMOS Input Voltage             | -0.3 | V <sub>DD</sub> +0.3 | V    |

| LVDS Input Voltage               | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Junction Temperature             | -    | 125                  | °C   |

| Storage Temperature              | -55  | 125                  | °C   |

| Reflow Peak Temperature / Time   | -    | 260 / 10sec          | °C   |

| Maximum Power Dissipation @+25°C | -    | 2.5                  | W    |

# **Operating Conditions**

**Table 5. Operating Condition**

| Symbol                      | Paramete                  | Min        | Тур | Max | Unit |        |

|-----------------------------|---------------------------|------------|-----|-----|------|--------|

| Ta                          | Operating Ambient T       | emperature | -40 | 25  | +85  | °C     |

| V <sub>DD</sub>             | Power Supply Voltage      | ge         | 3.0 | 3.3 | 3.6  | V      |

|                             | Dual-In/Dual-Out          | Input      | 20  | -   | 85   | MHz    |

|                             | Duai-III/Duai-Out         | Output     | 20  | -   | 85   | WITIZ  |

|                             | Distribution              | Input      | 20  | -   | 85   | MHz    |

| E                           |                           | Output     | 20  | -   | 85   | WILIZ  |

| $\mathbf{F}_{\mathrm{clk}}$ | Single In/Duel Out        | Input      | 40  | -   | 135  | MHz    |

|                             | Single-In/Dual-Out        | Output     | 20  | -   | 67.5 | WITIZ  |

|                             | Dual In/Single Out        | Input      | 20  | -   | 42.5 | MHz    |

|                             | Dual-In/Single-Out Output |            | 40  | -   | 85   | IVITIZ |

## Power Consumption

## **Table 6. Power Consumption**

| Symbol | Parameter                             |                    | Conditions           |        | Min | Тур. | Max | Unit |

|--------|---------------------------------------|--------------------|----------------------|--------|-----|------|-----|------|

|        |                                       |                    | CLKIN=40MHz          |        | -   | -    | 265 |      |

|        |                                       | Dual-In/Dual-Out   | CLKIN=65MHz          |        | -   | -    | 305 | A    |

|        |                                       |                    | CLKIN=75MHz          |        | -   | -    | 325 | mA   |

|        |                                       |                    | CLKIN=85MHz          |        | -   | ı    | 340 |      |

|        |                                       |                    | CLKIN=40MHz          |        | -   | -    | 215 |      |

|        |                                       | Distribution       | CLKIN=65MHz          |        | -   | ı    | 235 | A    |

|        | Distribution                          | CLKIN=75MHz        | $R_{L Tx}=100\Omega$ | -      | -   | 245  | mA  |      |

|        | Operating Current                     |                    | CLKIN=85MHz          | L_IX   | -   | ı    | 260 |      |

| T      | I <sub>CCW</sub> (Worst Case Pattern) |                    | CLKIN=40MHz          | CL=5pF | -   | 1    | 175 |      |

| 1CCW   |                                       | CLKIN=65MHz        | RS=VDD               | -      | ı   | 190  |     |      |

|        | Fig 5.                                | Single-In/Dual-Out | CLKIN=75MHz          |        | -   | 1    | 200 | mA   |

|        |                                       | Single-in/Dual-Out | CLKIN=85MHz          | Fig 6. | -   | ı    | 210 |      |

|        |                                       |                    | CLKIN=112MHz         |        | 1   | -    | 230 |      |

|        |                                       |                    | CLKIN=135MHz         |        | -   | -    | 250 |      |

|        |                                       |                    | CLKIN=20MHz          |        | -   | -    | 215 |      |

|        |                                       | Dual In/Single Out | CLKIN=32.5MHz        |        | -   | ı    | 235 | mA   |

|        |                                       | Dual-In/Single-Out | CLKIN=37.5MHz        |        | -   | 1    | 245 |      |

|        |                                       |                    | CLKIN=42.5MHz        |        | -   | -    | 260 |      |

| Iccs   | Power Down Current                    | -                  | -                    | -      | -   | -    | 8   | mA   |

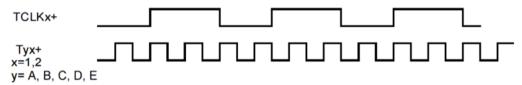

**Figure 5. Test Pattern (LVDS Output Full Toggle Pattern)**

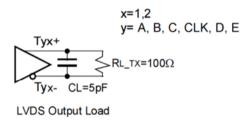

Figure 6. LVDS Output Load

## **Electrical Characteristics**

# **DC Specifications**

## **Table 7. DC Specifications**

| Symbol              | Parameter                        | Conditions              | Min | Тур | Max | Unit |

|---------------------|----------------------------------|-------------------------|-----|-----|-----|------|

| VCAP                | Capacitor pin appearance voltage | C <sub>CAP</sub> =0.1μF | -   | 1.8 | -   | V    |

| V <sub>IL</sub>     | LV-TTL Input Low Voltage         | -                       | GND | -   | 0.8 | V    |

| V <sub>IH</sub>     | LV-TTL Input High Voltage        | -                       | 2.0 | -   | VDD | V    |

| I <sub>IN_TTL</sub> | LV-TTL Input Leakage Current     | -                       | -4  | -   | +4  | μА   |

# **LVDS Receiver DC Specifications**

## **Table 8. LVDS Receiver DC Specifications**

| Symbol                           | Parameter                           | Conditions               | Min  | Тур | Max  | Unit |

|----------------------------------|-------------------------------------|--------------------------|------|-----|------|------|

| V <sub>IN_RX</sub>               | LVDS-Rx Input Voltage Range         | -                        | 0.3  | -   | 2.1  | X7.  |

| V <sub>IC_RX</sub>               | LVDS-Rx Common Voltage              | -                        | 0.6  | 1.2 | 1.8  | V    |

| V <sub>TH_RX</sub>               | LVDS-Rx Differential High Threshold | V - 12V                  | -    | -   | +100 |      |

| V <sub>TL_RX</sub>               | LVDS-Rx Differential Low Threshold  | $V_{IC\_RX} = 1.2V$      | -100 | -   | -    | mV   |

| $ \mathbf{V}_{\mathbf{ID\_RX}} $ | LVDS-Rx Differential Input Voltage  | -                        | 100  | -   | 600  |      |

|                                  |                                     | PD=VDD                   | -0.3 | -   | +0.3 | mA   |

| I <sub>IN_RX</sub>               | LVDS-Rx Input Leakage Current       | PD=GND<br>Vin=GND or VDD | -10  | -   | +10  | μΑ   |

# **LVDS Transmitter DC Specifications**

## **Table 9. LVDS Transmitter DC Specifications**

| Symbol              | Parameter                                         | Conditions            |                              | Min          | Тур  | Max   | Unit |

|---------------------|---------------------------------------------------|-----------------------|------------------------------|--------------|------|-------|------|

| Voc_tx              | LVDS-Tx Common Voltage                            |                       | -                            | 1.125        | 1.25 | 1.375 | V    |

| ΔV <sub>OC_TX</sub> | Change in VOC between complementary output states | $R_{L_TX} =$          | -                            | -            | -    | 35    | mV   |

| I <b>T</b> 7        | LVDS-Tx Differential                              |                       | R <sub>L_TX</sub> = 100Ω     | Normal Swing | 250  | 350   | 450  |

| VOD_TX              | OD_TX Output Threshold                            | 10052                 | Reduced Swing                | 100          | 200  | 300   | mV   |

| $\Delta V_{OD\_TX}$ | Change in VOD between complementary output states |                       | -                            | -            | -    | 35    | mV   |

| Ios_tx              | LVDS-Tx Output Short Current                      | V <sub>DD</sub> =3.3V | V <sub>out</sub> =GND        | -24          | -    | -     | mA   |

| Ioz_tx              | LVDS-Tx Output Tri-state Current                  | PD=GND                | V <sub>out</sub> =GND to VDD | -10          | -    | +10   | μΑ   |

# **AC Specifications**

**Table 10. AC Specifications**

| Symbol           | Parameter                         | Cond               | itions        | Min                         | Тур                                     | Max                         | Unit |

|------------------|-----------------------------------|--------------------|---------------|-----------------------------|-----------------------------------------|-----------------------------|------|

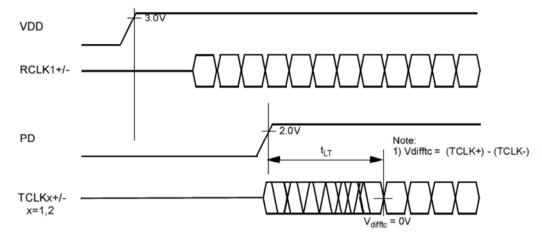

| t <sub>LT</sub>  | Phase Lock Loop Set Time (Fig 7.) | -                  | -             | -                           | -                                       | 10                          | ms   |

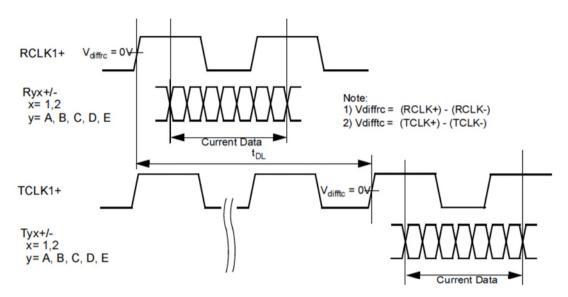

|                  |                                   | Dual-In/Dual-Out   | CLKIN=75MHz   | 9t <sub>RCP</sub> +3        | 9t <sub>RCP</sub> +5                    | 9t <sub>RCP</sub> +7        |      |

|                  | D-4- I -4 (E' 9 )                 | Distribution       | CLKIN=75MHz   | 9t <sub>RCP</sub> +3        | 9t <sub>RCP</sub> +5                    | 9t <sub>RCP</sub> +7        |      |

| tdl              |                                   | Single-In/Dual-Out | CLKIN=75MHz   | (11+2/7)t <sub>RCP</sub> +3 | (11+2/7)t <sub>RCP</sub> +5             | (11+2/7)t <sub>RCP</sub> +7 | ns   |

|                  |                                   | Dual-In/Single-Out | CLKIN=37.5MHz | (8+5/14)t <sub>RCP</sub> +3 | (8+5/14)t <sub>RCP</sub> +5             | (8+5/14)t <sub>RCP</sub> +7 |      |

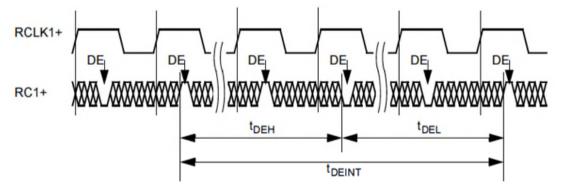

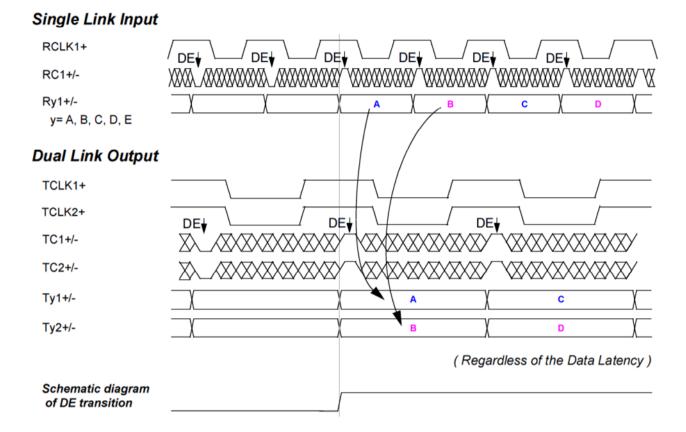

| tdeh             | DE Input High Time (Fig 9.)       |                    | -             | $2t_{RCP}$                  | -                                       | -                           |      |

| t <sub>DEL</sub> | DE Input Low Time (Fig 9.)        | Single-In/Dual-Out | -             | 2t <sub>RCP</sub>           | -                                       | -                           | ns   |

| tdeint           | DE Input Period (Fig 9.)          |                    | -             | 4t <sub>RCP</sub>           | Must be 2n t <sub>RCP</sub> (n=integer) | -                           |      |

# **AC Timing Diagrams**

Figure 7. Phase Lock Loop Set Time

## AC Timing Diagrams (Continued)

Figure 8. DATA Latency

Figure 9. Single Link Input / Dual Link Output Mode RC1(DE) Input Timing

# **LVDS Receiver AC Specifications**

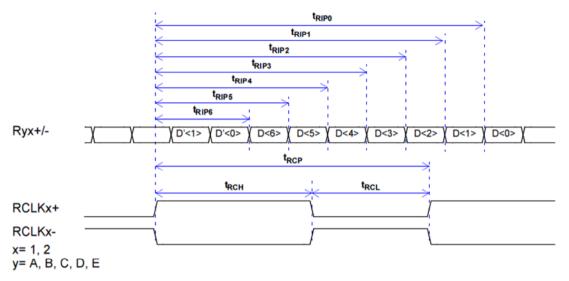

**Table 11. LVDS Receiver AC Specifications**

| Symbol            | Parameter                            | Conditions                  | Min                                    | Тур                 | Max                                    | Unit |

|-------------------|--------------------------------------|-----------------------------|----------------------------------------|---------------------|----------------------------------------|------|

| t <sub>RCP</sub>  | LVDS Clock Period                    | -                           | 7.4                                    | -                   | 50                                     |      |

| trch              | LVDS Clock High Duration             | -                           | 2/7t <sub>RCP</sub>                    | 4/7t <sub>RCP</sub> | 5/7t <sub>RCP</sub>                    | ns   |

| $t_{ m RCL}$      | LVDS Clock Low Duration              | -                           | 2/7t <sub>RCP</sub>                    | 3/7t <sub>RCP</sub> | 5/7t <sub>RCP</sub>                    |      |

|                   |                                      | CLKIN=75MHz <sup>(1)</sup>  | 480                                    | -                   | -                                      |      |

| $t_{RSUP}$        | LVDS Data Input Setup Margin         | CLKIN=112MHz <sup>(1)</sup> | 250                                    | -                   | -                                      | ps   |

|                   |                                      | CLKIN=135MHz <sup>(1)</sup> | 220                                    | -                   | -                                      |      |

|                   |                                      | CLKIN=75MHz <sup>(1)</sup>  | 480                                    | -                   | -                                      |      |

| $t_{ m RHLD}$     | LVDS Data Input Hold Margin          | CLKIN=112MHz <sup>(1)</sup> | 250                                    | -                   | -                                      | ps   |

|                   |                                      | CLKIN=135MHz <sup>(1)</sup> | 220                                    | -                   | -                                      |      |

| t <sub>RIP6</sub> | LVDS Data Input Position 6           | -                           | 2/7trcp-trhld                          | 2/7t <sub>RCP</sub> | 2/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

| trip5             | LVDS Data Input Position 5           | -                           | 3/7trcp-trhld                          | 3/7t <sub>RCP</sub> | 3/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

| trip4             | LVDS Data Input Position 4           | -                           | 4/7t <sub>RCP</sub> -t <sub>RHLD</sub> | 4/7t <sub>RCP</sub> | 4/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

| t <sub>RIP3</sub> | LVDS Data Input Position 3           | -                           | 5/7t <sub>RCP</sub> -t <sub>RHLD</sub> | 5/7t <sub>RCP</sub> | 5/7t <sub>RCP</sub> +t <sub>RSUP</sub> | ps   |

| t <sub>RIP2</sub> | LVDS Data Input Position 2           | -                           | 6/7trcp-trhld                          | 6/7t <sub>RCP</sub> | 6/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

| $t_{ m RIP1}$     | LVDS Data Input Position 1           | -                           | 7/7t <sub>RCP</sub> -t <sub>RHLD</sub> | 7/7t <sub>RCP</sub> | 7/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

| t <sub>RIP0</sub> | LVDS Data Input Position 0           | -                           | 8/7t <sub>RCP</sub> -t <sub>RHLD</sub> | 8/7t <sub>RCP</sub> | 8/7t <sub>RCP</sub> +t <sub>RSUP</sub> |      |

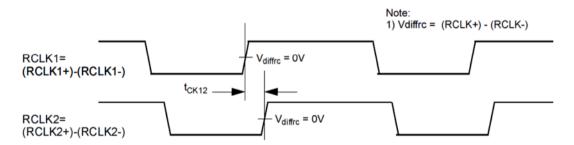

| t <sub>CK12</sub> | Skew Time Between<br>RCLK1 and RCLK2 | -                           | -0.3 t <sub>RCP</sub>                  | -                   | +0.3 t <sub>RCP</sub>                  | ps   |

<sup>(1)</sup> V<sub>IC\_RX</sub>=1.2V, t<sub>RCH</sub>=4/7 t<sub>RCP</sub>

#### LVDS Receiver Input Timing

Ry1+/- skew margin is the one between RCLK1+/- and Ry1+/-. Ry2+/- skew margin is the one between RCLK2+/- and Ry2+/-.

Figure 10. LVDS Receiver Timing

Figure 11. Skew time between RCLK1 and RCLK2

# LVDS Transmitter AC Specifications

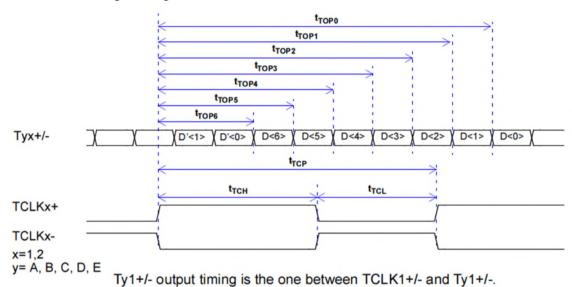

**Table 12. LVDS Transmitter AC Specifications**

| Symbol            | Parameter                      | Conditions   | Min                                    | Тур                 | Max                                    | Unit |

|-------------------|--------------------------------|--------------|----------------------------------------|---------------------|----------------------------------------|------|

| t <sub>TCP</sub>  | LVDS Clock Period              | -            | 11.76                                  | -                   | 50                                     |      |

| <b>t</b> TCH      | LVDS Clock High Duration       | -            | -                                      | 4/7t <sub>TCP</sub> | -                                      | ns   |

| t <sub>TCL</sub>  | LVDS Clock Low Duration        | -            | -                                      | 3/7t <sub>TCP</sub> | -                                      |      |

| ttsup             | LVDS Data Output Setup         | CLKOUT=75MHz | -                                      | -                   | 250                                    | ps   |

| t <sub>THLD</sub> | LVDS Data Output Hold          | CLKOUT=75MHz | -                                      | -                   | 250                                    | ps   |

| <b>t</b> тор6     | LVDS Data Output Position 6    | -            | 2/7t <sub>TCP</sub> -t <sub>THLD</sub> | 2/7t <sub>TCP</sub> | 2/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

| t <sub>TOP5</sub> | LVDS Data Output Position 5    | -            | 3/7t <sub>TCP</sub> -t <sub>THLD</sub> | 3/7t <sub>TCP</sub> | 3/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

| t <sub>TOP4</sub> | LVDS Data Output Position 4    | -            | 4/7t <sub>TCP</sub> -t <sub>THLD</sub> | 4/7t <sub>TCP</sub> | 4/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

| <b>t</b> торз     | LVDS Data Output Position 3    | -            | 5/7t <sub>TCP</sub> -t <sub>THLD</sub> | 5/7t <sub>TCP</sub> | 5/7t <sub>TCP</sub> +t <sub>TSUP</sub> | ps   |

| t <sub>TOP2</sub> | LVDS Data Output Position 2    | -            | 6/7t <sub>TCP</sub> -t <sub>THLD</sub> | 6/7t <sub>TCP</sub> | 6/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

| t <sub>TOP1</sub> | LVDS Data Output Position 1    | -            | 7/7t <sub>TCP</sub> -t <sub>THLD</sub> | 7/7t <sub>TCP</sub> | 7/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

| t <sub>TOP0</sub> | LVDS Data Output Position 0    | -            | 8/7t <sub>TCP</sub> -t <sub>THLD</sub> | 8/7t <sub>TCP</sub> | 8/7t <sub>TCP</sub> +t <sub>TSUP</sub> |      |

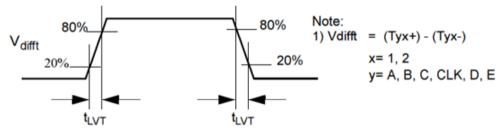

| t <sub>LVT</sub>  | LVDS Transition Time (Fig 13.) | Fig.6        | -                                      | 0.6                 | 1.5                                    | ns   |

## LVDS Transmitter Output Diagram

Ty2+/- output timing is the one between TCLK2+/- and Ty2+/-.

Figure 12. LVDS Transmitter Timing

**Figure 13. LVDS Transition Timing**

## **LVDS Data Mapping**

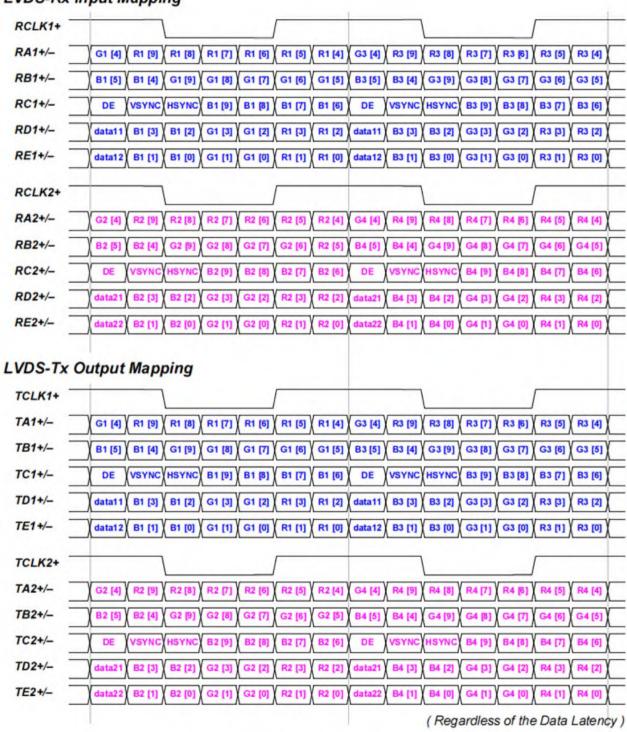

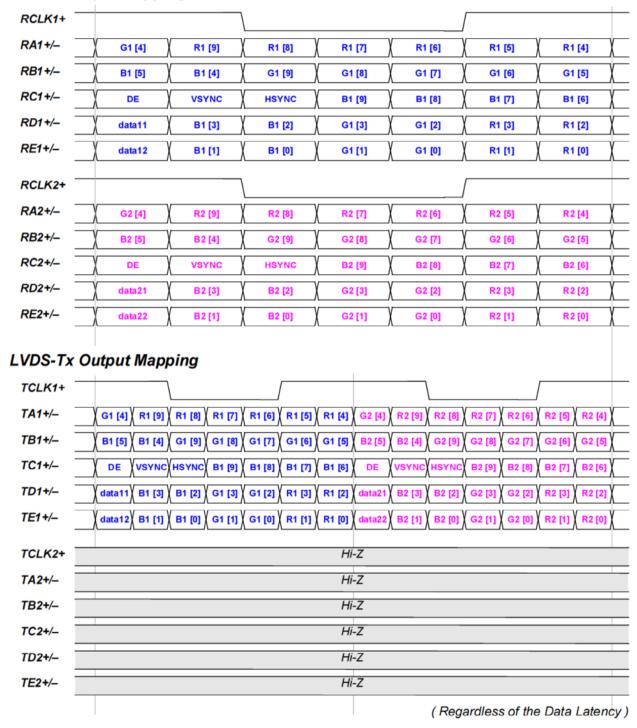

## **Dual-In / Dual-Out**

## LVDS-Rx Input Mapping

Data bits "data11, data12, data21, data22" are available for additional data transmission.

Figure 14-1. Data Mapping for Dual-In/Dual-Out

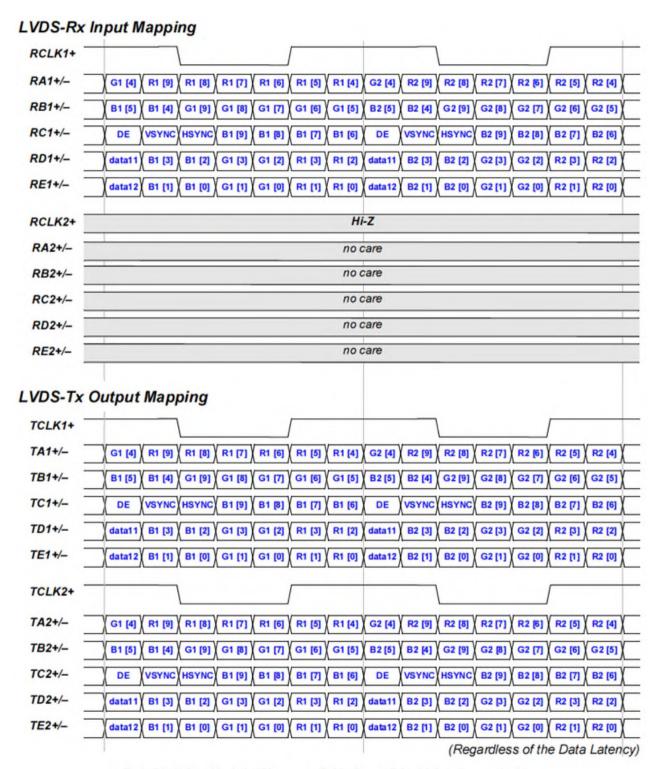

#### **Distribution Mode**

In Distribution mode, RCLK2+/- must be Hi-Z.

Data bits "data11, data12" are available for additional data transmission.

Figure 14-2. Data Mapping for Distribution mode

#### Single-In / Dual-Out

In Single-in / Dual-out mode, RCLK2+/- must be Hi-Z.

# LVDS-Rx Input Mapping RCLK1+

Data bits "data11, data12" are available for additional data transmission.

Figure 14-3(a). Data Mapping for Single-In/Dual-Out

Single-in / Dual-out mode uses DE signal L-to-H-edge to start distribution of input data.

Figure 14-3(b). Data Mapping for Single-In/Dual-Out

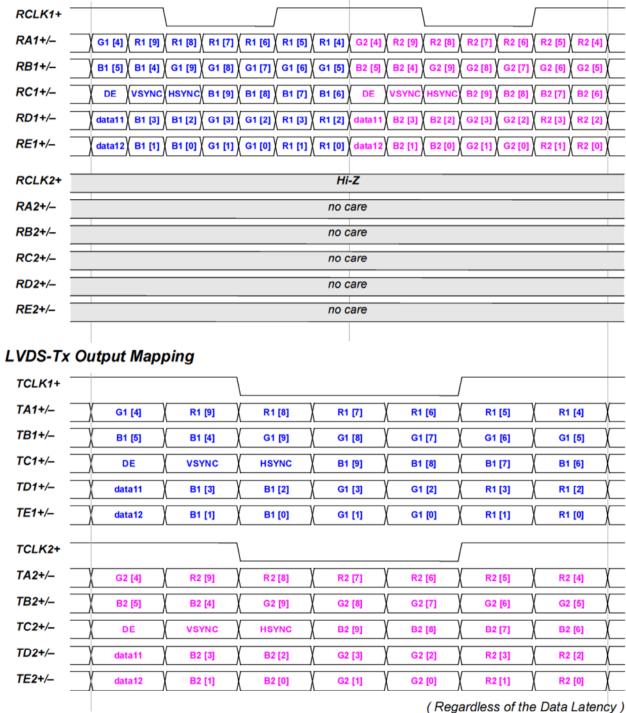

#### **Dual-In / Single-Out**

#### LVDS-Rx Input Mapping

Data bits "data11, data12, data21, data22" are available for additional data transmission.

Figure 14-4. Data Mapping for Dual-In/Single-Out

#### Notes

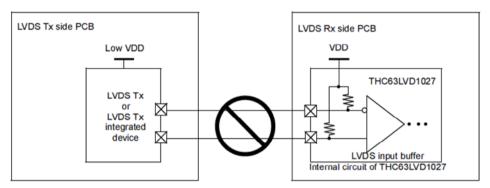

## 1) LVDS input pin connection

When LVDS line is not derived from the previous device, the line is pulled up to 3.3V internally in THC63LVD1027. This can cause violation of absolute maximum ratings to the previous LVDS Tx device whose operating condition is lower voltage power supply than 3.3V. This phenomenon may happen at power on phase of the whole system including THC63LVD1027. One solution for this problem is PD=L control during no LVDS input period because pull-up resistors are cut off at power down state.

Figure 15. LVDS input pin connection

#### 2) Power On Sequence

Don't input RCLK1+/- and RCLK2+/- before THC63LVD1027 is on in order to keep absolute maximum ratings.

#### 3) Cable Connection and Disconnection

Don't connect and disconnect the LVDS cable, when the power is supplied to the system.

#### 4) GND Connection

Connect the each GND of the PCB which Transmitter, Receiver and THC63LVD1027 on it. It is better for EMI reduction to place GND cable as close to LVDS cable as possible.

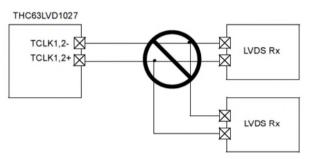

#### 5) Multi Drop Connection

Multi drop connection is not recommended.

**Figure 16.Multi Drop Connection**

#### 6) Asynchronous use

Asynchronous use such as following systems are not recommended. Page.11 tCK12 spec should be kept.

Figure 17-1. Asynchronous Use1

Asynchronous use such as following systems are not recommended.

Figure 17-2. Asynchronous Use2

#### 7) De-coupling capacitor

THC63LVD1027 requires appropriate de-coupling capacitor placement on VDD. Especially, VDD pin 36 and pin 61 requires 0.1uF and 4.7nF capacitor parallel placement close to IC pins.

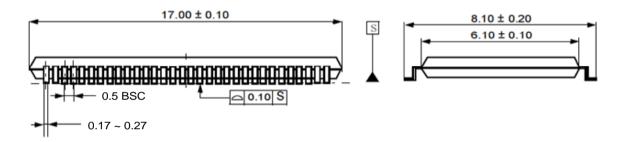

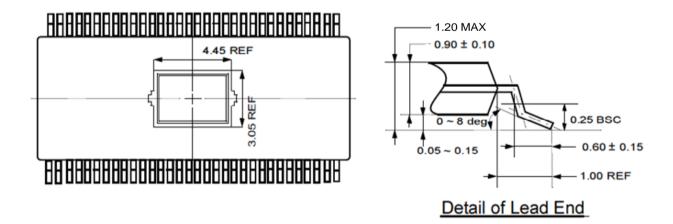

#### **Package**

Unit: mm

Exposed PAD is GND and must be soldered to PCB.

Figure 18. Package Diagram

#### Notices and Requests

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other intellectual property rights. Copying, reverse-engineer or disclosing to third parties the contents of this material without THine's prior written permission is prohibited.

- 4. THINE ACCEPTS NO LIABILITY FOR ANY DAMAGE OR LOSS IN CONNECTION WITH ANY DISPUTE RELATING TO INTELLECTUAL PROPERTY RIGHTS BETWEEN THE USER AND ANY THIRD PARTY, ARISING OUT OF THIS PRODUCT, EXCEPT FOR SUCH DAMAGE OR LOSS IN CONNECTION WITH DISPUTES SUCCESSFULLY PROVED BY THE USER THAT SUCH DISPUTES ARE DUE SOLELY TO THINE. NOTE, HOWEVER, EVEN IN THE AFOREMENTIONED CASE, THINE ACCEPTS NO LIABILITY FOR SUCH DAMAGE OR LOSS IF THE DISPUTE IS CAUSED BY THE USER'S INSTRUCTION.

- 5. This product is not designed for applications that require extremely high-reliability/safety such as aerospace device, nuclear power control device, or medical device related to critical care, excluding when this product is specified for automotive use by THine and used it for that purpose. THine accepts no liability whatsoever for any damages, claims or losses arising out of the uses set forth above.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently fail-safe design principles such as redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. This product may be permanently damaged and suffer from performance degradation or loss of mechanical functionality if subjected to electrostatic charge exceeding capacity of the ESD (Electrostatic Discharge) protection circuitry. Safety earth ground must be provided to anything in contact with the product, including any operator, floor, tester and soldering iron.

- 8. Please note that this product is not designed to be radiation-proof.

- 9. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 10. This product must be stored according to storage method which is specified in this specifications. Thine accepts no liability whatsoever for any damage or loss caused to the user due to any storage not according to above-mentioned method.

- 11. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act in Japan and the Export Administration Regulations in the United States of America on export or transit of this product. This product is prohibited for the purpose of developing military modernization, including the development of weapons of mass destruction (WMD), and the purpose of violating human rights.

- 12. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses. Thine accepts no liability whatsoever for any damage or loss caused to the user due to use under a condition exceeding the limiting values.

- 13. All patents or pending patent applications, trademarks, copyrights, layout-design exploitation rights or other intellectual property rights concerned with this product belong to Thine or licensor(s) of Thine. No license or right is granted to the user for any intellectual property right or other proprietary right now or in the future owned by Thine or Thine's licensor. The user must enter into a license agreement with Thine or Thine's licensor to be granted of such license or right.

# THine Electronics, Inc.

https://www.thine.co.jp