# **THCV2712**

V-by-One® HS Distributor

### **General Description**

The THCV2712 is a high performance 1:2 signal distributor for V-by-One® HS with data rates up to 4Gbps and integrated 2:1 and 1:2 signal switcher support bi-directional communication.

The THCV2712 features the distribution function which duplicates a V-by-One<sup>®</sup> HS signal and the switch function which changes the path of signals. All configurations are supported by external pins.

All driver outputs and receiver inputs are internally terminated which no require external components.

#### **Features**

- Unidirectional Distribution

- Bi-directional Switch (1:2 and 2:1)

- Transmit VOD Control: 600 to 1300 mVp-p

- Available in single supply voltage 3.3V with integrated LDO

- ESD: HBM ±4kV

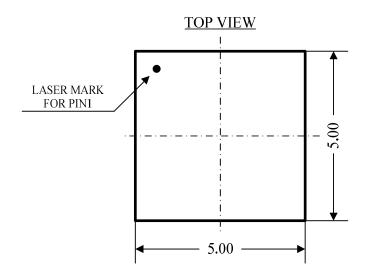

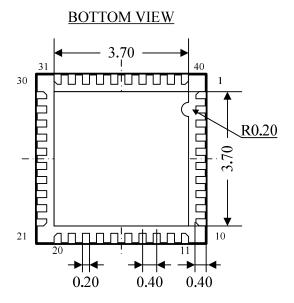

- QFN40 (5.0mm x 5.0mm)

#### **Applications**

All V-by-One® HS applications such as

- Digital Signage

- Digital Blackboard

- Multi-Function Printer

- Production Printer

- Medical Imaging

- Machine Vision

- Image Sensor

- Camera

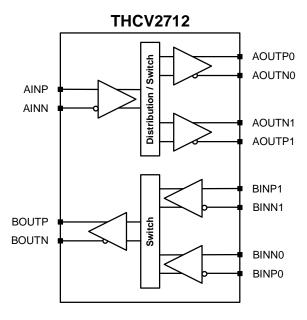

#### **Block Diagram**

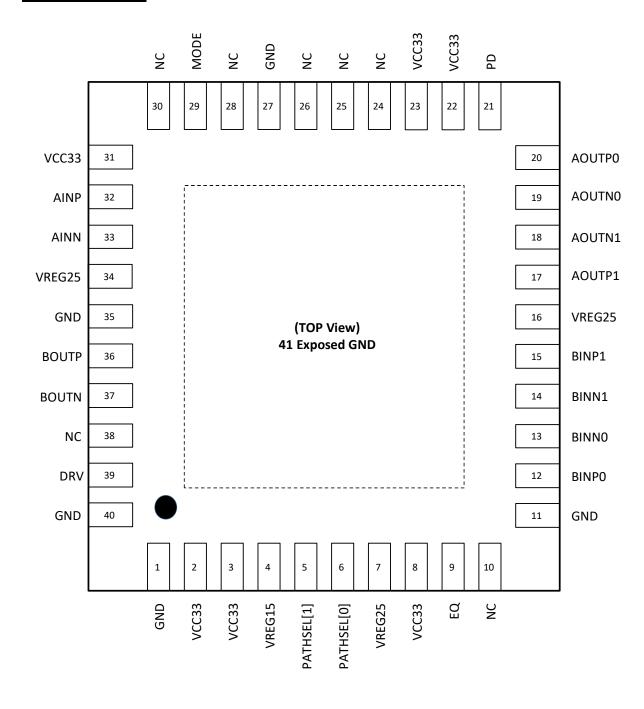

# **Pin Configuration**

**Pin Description**

| i ili Description |                              |      |                                                                                                      |

|-------------------|------------------------------|------|------------------------------------------------------------------------------------------------------|

| Pin Name          | Pin No                       | Туре | Description                                                                                          |

| AINP              | 32                           | CI   | High-Speed CML Channel A (CHA) Signal Input                                                          |

| AINN              | 33                           | CI   | High-Speed CML Channel A (CHA) Signal Input                                                          |

| BOUTP             | 36                           | CO   | High-Speed CML Channel B (CHB) Signal Output                                                         |

| BOUTN             | 37                           | СО   | High-Speed CML Channel B (CHB) Signal Output                                                         |

| AOUTP1            | 17                           | CO   | High-Speed CML Port 1 of CHA Signal Output                                                           |

| AOUTN1            | 18                           | CO   | High-Speed CML Port 1 of CHA Signal Output                                                           |

| AOUTP0            | 20                           | CO   | High-Speed CML Port 0 of CHA Signal Output                                                           |

| AOUTN0            | 19                           | CO   | High-Speed CML Port 0 of CHA Signal Output                                                           |

| BINP1             | 15                           | CI   | High-Speed CML Port 1 of CHB Signal Input                                                            |

| BINN1             | 14                           | CI   | High-Speed CML Port 1 of CHB Signal Input                                                            |

| BINP0             | 12                           | CI   | High-Speed CML Port 0 of CHB Signal Input                                                            |

| BINN0             | 13                           | CI   | High-Speed CML Port 0 of CHB Signal Input                                                            |

| PD                | 21                           | I    | Power Down 0: Operation 1: Chip Power Down                                                           |

| MODE              | 29                           | I    | Mode select 0 : Distribution 1 : Switch                                                              |

| PATHSEL[1:0]      | 5,6                          | 1    | Select Switch Input / Output                                                                         |

| EQ                | 9                            | 3LI  | Rx equalizer setting.                                                                                |

| DRV               | 39                           | 3LI  | Tx output swing control                                                                              |

| VREG15            | 4                            | PWR  | Decoupling Capacitor Pin for On-chip Regulator.                                                      |

| VREG25            | 7,16,34                      | PWR  | Decoupling Capacitor Pin, 2.5V output.                                                               |

| VCC33             | 2,3,8,22,<br>23,31           | PWR  | Power supply pin for on-chip regulator.                                                              |

| GND               | 1,11,27,<br>35,40,41         | GND  | Ground. Must be tied to the PCB ground plane through an array of vias. Pin#41 is exposed pad ground. |

| NC                | 10,24,25,<br>26,28,30,<br>38 | NC   | Non-connection pin. Must be open.                                                                    |

CI: CML Input buffer, CO: CML Output buffer

I: LVCMOS Input buffer, 3LI: 3-Level LVCMOS Input buffer, PWR: Power supply, GND: Ground, NC: Non-connection pin

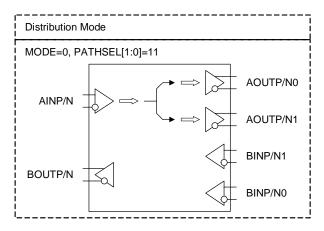

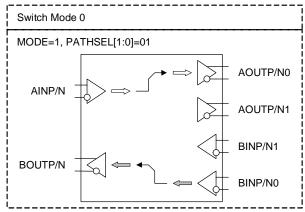

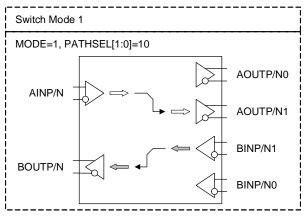

# **Operation Mode Settings**

Table1 shows the operation mode setting.

**Table 1. Operation Mode Setting**

|    | Pin Settings |              | Operation Mode            |

|----|--------------|--------------|---------------------------|

| PD | MODE         | PATHSEL[1:0] | Operation Mode            |

|    | 0            | 11           | Distribution Mode         |

| 0  | 4            | 01           | Switch Mode Port 0 Enable |

|    | '            | 10           | Switch Mode Port 1 Enable |

| 1  | Ignore       | Ignore       | Chip Power Down.          |

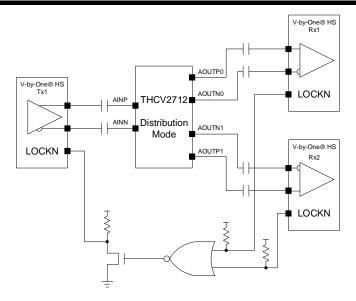

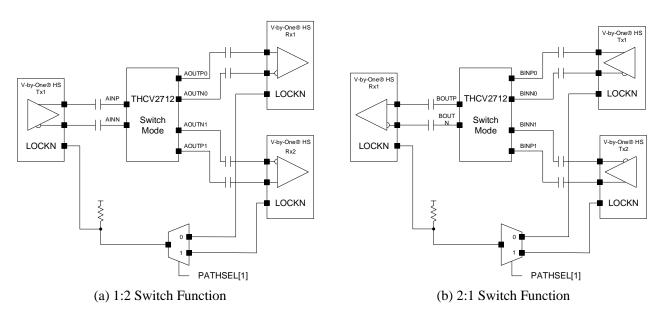

LOCKN/HTPDN signals are not be distributed and switched. The signals should be bypassed THCV2712.

Figure 1. LOCKN circuits in Distribution Mode

Figure 2. LOCKN circuits in Switch Mode

# **Absolute Maximum Ratings**

**Table 2. Absolute Maximum Ratings**

| Par                   | ameter                       | Min  | Тур | Max       | Unit   |

|-----------------------|------------------------------|------|-----|-----------|--------|

| Supply Vo             | Supply Voltage(VCC33)        |      |     | 4.0       | V      |

|                       | Input Voltage                | -0.3 | -   | VCC33+0.3 | V      |

|                       | CMOS Input Voltage           | -0.3 | -   | VCC33+2.5 | V      |

|                       | 3-Level LVCMOS Input Voltage |      |     | VCC33+0.3 | V      |

|                       | CML Receiver Input Voltage   |      |     | 3.0       | V      |

| CML Transmitt         | er Output Voltage            | -0.3 | -   | 3.0       | V      |

| ESD Rating            | HBM                          | -    | -   | ±4        | kV     |

| E3D Rating            | CDM                          | -    | -   | ±500      | V      |

| Storage <sup>-</sup>  | Storage Temperature          |      |     | 125       | Ô      |

| Junction <sup>1</sup> | -                            | -    | 125 | Ô         |        |

| Reflow Peak 1         | emperature/Time              | -    | -   | 260/10    | °C/sec |

# **Recommended Operating Conditions**

**Table 3. Recommended Operating Condition**

| Parameter               | Min | Тур | Max | Unit |

|-------------------------|-----|-----|-----|------|

| Supply Voltage(VCC33)   | 3.0 | 3.3 | 3.6 | V    |

| Supply Ramp Requirement | 0.1 | -   | 50  | ms   |

| Operating Temperature   | -40 | -   | 85  | °C   |

# **Electrical Specification**

LVCMOS DC Specification

### **Table 4. LVCMOS DC Specification**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter                                 | Condition             | Min | Тур | Max   | Unit |

|--------|-------------------------------------------|-----------------------|-----|-----|-------|------|

| VIH    | High Level Input Voltage                  | -                     | 2.0 | -   | VCC33 | V    |

| VIL    | Low Level Input Voltage                   | -                     | 0   | -   | 0.7   | V    |

| VOH    | High Level Output Voltage                 | I <sub>oh</sub> =-2mA | 2.4 | -   | VCC33 | V    |

| VOL    | Low Level Output Voltage                  | I <sub>ol</sub> =8mA  | 0   | -   | 0.4   | V    |

| IOZH   | Output Leak Current High in Hi-Z<br>State | -                     | -15 | -   | 15    | uA   |

| IOZL   | Output Leak Current Low in Hi-Z State     | -                     | -15 | -   | 15    | uA   |

#### 3-Level LVCMOS DC Specification

#### Table 5. 3-Level LVCMOS DC Specification

Over recommended operating supply and temperature range unless otherwise specified

| Symbol             | Parameter                     | Condition | Min  | Тур  | Max  | Unit |

|--------------------|-------------------------------|-----------|------|------|------|------|

| V <sub>THL</sub>   | Low-Level Threshold Voltage   | *         | 0.42 | 0.83 | 1.25 | V    |

| Vтнн               | High-Level Threshold Voltage  | *         | 1.25 | 1.67 | 2.08 | V    |

| I <sub>IH_3L</sub> | High Level Input Leak Current | VIN=VCC33 | -100 | -    | 100  | uA   |

| I <sub>IL_3L</sub> | Low Level Input Leak Current  | VIN=GND   | -100 | -    | 100  | uA   |

<sup>\*</sup>Must be tied for setting each level

Low: Tie 1k  $\Omega$   $\pm 5\%$  to GND

Float: Leave pin open

High: Tie 1k  $\Omega$  ±5% to VCC33

#### Supply Current

#### **Table 6. Supply Current**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter                  | Condition                          | Min | Тур | Max | Unit |

|--------|----------------------------|------------------------------------|-----|-----|-----|------|

|        |                            | PD=0,MODE=1<br>EQ=High<br>DRV=High | -   | -   | 170 | mA   |

| ICCW   | Active Mode Supply Current | PD=0,MODE=1<br>EQ=Low<br>DRV=Low   | -   | 90  | -   | mA   |

|        |                            | PD=0,MODE=0                        | -   | -   | 250 | mA   |

| ICCS   | Power Down Supply Current  | PD=1                               | -   | 1.0 | 2.0 | mA   |

### Receiver DC/AC Specification

### Table 7. Receiver DC/AC Specification

Over recommended operating supply and temperature range unless otherwise specified

| Symbol                   | Parameter                         | Condition | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------|-----------|-----|-----|-----|------|

| V <sub>RX-TH</sub>       | CML Differential Input High       |           |     |     | 50  | mV   |

| V RX-1H                  | Threshold                         |           | _   | -   | 30  | IIIV |

| $V_{RX-TL}$              | CML Differential Input Low        |           | -50 | _   | _   | mV   |

| V RX-IL                  | Threshold                         |           | -30 | _   | _   | IIIV |

| $V_{RX-RIN}$             | CML Differential Input Resistance |           | 80  | 100 | 120 | Ω    |

| V <sub>RX-EQ-LOW</sub>   | Input Equalization@2GHz           | EQ=Low    | -   | 3.2 | -   | dB   |

| V <sub>RX-EQ-FLOAT</sub> | Input Equalization@2GHz           | EQ=Float  | -   | 4.6 | -   | dB   |

| V <sub>RX-EQ-HIGH</sub>  | Input Equalization@2GHz           | EQ=High   | -   | 7.6 | -   | dB   |

# Transmitter DC / AC specifications

### Table 8. Transmitter DC / AC specification

Over recommended operating supply and temperature range unless otherwise specified

| Currente a l                  | Devementer                              | Condition | Min | Time | Max | l lm!4 |

|-------------------------------|-----------------------------------------|-----------|-----|------|-----|--------|

| Symbol                        | Parameter                               | Condition | Min | Тур  | Max | Unit   |

| VTX-DIFF-PP-LOW               | Differential p-p Tx Voltage<br>Swing    | DRV=Low   | 0.4 | 0.6  | 0.8 |        |

| V <sub>TX-DIFF-PP-FLOQT</sub> | Differential p-p Tx Voltage<br>Swing    | DRV=Float | 0.8 | 1.0  | 1.2 | V      |

| VTX-DIFF-PP-HIGH              | Differential p-p Tx Voltage<br>Swing    | DRV=High  | 1.0 | 1.3  | 1.6 |        |

| R <sub>TX-DIFF-DC</sub>       | DC Differential Impedance               | -         | 80  | 100  | 120 | Ω      |

| Vтх-dc-см                     | Transmitter DC Common-mode Voltage      | -         | -   | 1.9  | -   | ٧      |

| ITX-SHORT                     | Transmitter Short-circuit Current Limit | -         | -   | 20   | 60  | mA     |

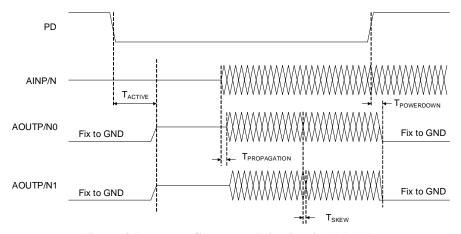

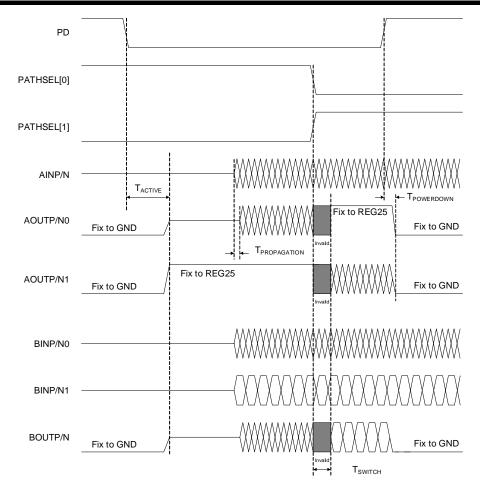

| TACTIVE                       | PD Low to CML Output Delay              |           |     |      | 200 | ns     |

| TPOWERDOWN                    | PD High to CML Output High Fix Delay    |           |     |      | 10  | ns     |

| T <sub>SKEW</sub>             | CML Output Inter-pair skew              |           |     |      | 25  | ps     |

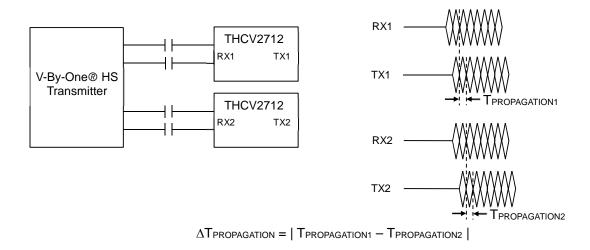

| T <sub>PROPAGATION</sub>      | Differential Propagation Delay          | -         | -   | 150  | -   | ps     |

| <b>ΔT</b> PROPAGATION         | Delta Propagation Delay                 |           | -   | -    | 90  | ps     |

| T <sub>SWITCH</sub>           | Switching Time                          | -         | -   | -    | 10  | ns     |

Figure 3 Power on Sequence (Distribution Mode)

Figure 4. Power on Sequence (Switch Mode)

Figure 5. CML Propagation Delay Timing

9/11

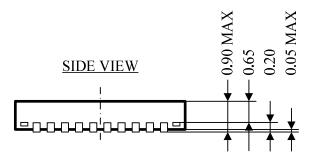

# **Package**

Unit: mm

Figure 6. 40-pin QFN package physical dimension

# **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other intellectual property rights. Copying, reverse-engineer or disclosing to third parties the contents of this material without THine's prior written permission is prohibited.

- 4. THINE ACCEPTS NO LIABILITY FOR ANY DAMAGE OR LOSS IN CONNECTION WITH ANY DISPUTE RELATING TO INTELLECTUAL PROPERTY RIGHTS BETWEEN THE USER AND ANY THIRD PARTY, ARISING OUT OF THIS PRODUCT, EXCEPT FOR SUCH DAMAGE OR LOSS IN CONNECTION WITH DISPUTES SUCCESSFULLY PROVED BY THE USER THAT SUCH DISPUTES ARE DUE SOLELY TO THINE. NOTE, HOWEVER, EVEN IN THE AFOREMENTIONED CASE, THINE ACCEPTS NO LIABILITY FOR SUCH DAMAGE OR LOSS IF THE DISPUTE IS CAUSED BY THE USER'S INSTRUCTION.

- 5. This product is not designed for applications that require extremely high-reliability/safety such as aerospace device, nuclear power control device, or medical device related to critical care, excluding when this product is specified for automotive use by THine and used it for that purpose. THine accepts no liability whatsoever for any damages, claims or losses arising out of the uses set forth above.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently fail-safe design principles such as redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. This product may be permanently damaged and suffer from performance degradation or loss of mechanical functionality if subjected to electrostatic charge exceeding capacity of the ESD (Electrostatic Discharge) protection circuitry. Safety earth ground must be provided to anything in contact with the product, including any operator, floor, tester and soldering iron.

- 8. Please note that this product is not designed to be radiation-proof.

- 9. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 10. This product must be stored according to storage method which is specified in this specifications. Thine accepts no liability whatsoever for any damage or loss caused to the user due to any storage not according to above-mentioned method.

- 11. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act in Japan and the Export Administration Regulations in the United States of America on export or transit of this product. This product is prohibited for the purpose of developing military modernization, including the development of weapons of mass destruction (WMD), and the purpose of violating human rights.

- 12. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses. Thin accepts no liability whatsoever for any damage or loss caused to the user due to use under a condition exceeding the limiting values.

- 13. All patents or pending patent applications, trademarks, copyrights, layout-design exploitation rights or other intellectual property rights concerned with this product belong to THine or licensor(s) of THine. No license or right is granted to the user for any intellectual property right or other proprietary right now or in the future owned by THine or THine's licensor. The user must enter into a license agreement with THine or THine's licensor to be granted of such license or right.

# THine Electronics, Inc.

https://www.thine.co.jp